设有三个处理机A,B和C。它们各有一个高速缓冲存储器CA,CB和CC,并各有一个主存储器MA,MB和MC,其性能如表2-5所示。假定三个处理机的指令系统相同,它们的指令执行时间与存储器平均存取周期成正比。如果执行某个程序时,所需的指令或数据在缓冲存储器中取到的概率是P=0.6,那么这三个处理机按处理速度由快到慢的顺序应当是 (59) 。当P=0.75时,则其顺序应当是(60)。当P=0.95时,则其顺序应当是(61)。当P=(62)时,处理机A和B的处理速度最接近。当P=(63)时,处理机B和C的处理速度

题目

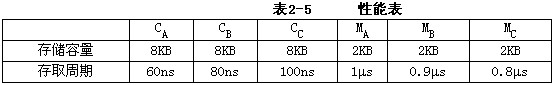

设有三个处理机A,B和C。它们各有一个高速缓冲存储器CA,CB和CC,并各有一个主存储器MA,MB和MC,其性能如表2-5所示。

假定三个处理机的指令系统相同,它们的指令执行时间与存储器平均存取周期成正比。如果执行某个程序时,所需的指令或数据在缓冲存储器中取到的概率是P=0.6,那么这三个处理机按处理速度由快到慢的顺序应当是 (59) 。

当P=0.75时,则其顺序应当是(60)。

当P=0.95时,则其顺序应当是(61)。

当P=(62)时,处理机A和B的处理速度最接近。

当P=(63)时,处理机B和C的处理速度最接近。

A.A,B,C

B.A,C,B

C.B,A,C

D.B,C,A

E.C,B,A

相似考题

更多“ 设有三个处理机A,B和C。它们各有一个高速缓冲存储器CA,CB和CC,并各有一个主存储器MA,MB和MC,其性能如表2-5所示。假定三个处理机的指令系统相同,它们的指令执行时间与存储器平均存取周期成正比。如果执行”相关问题

-

第1题:

在下列不同结构的处理机上执行6x6的矩阵乘法C:A×B,计算所需要的最短时间。只计算乘法指令和加法指令的执行时间,不计算取操作数、数据传送和程序控制等指令的执行时间。加法部件和乘法部件的延迟时间都是3个时钟周期,另外,加法指令和乘法指令还要经过“取指令”和“指令译码”的时钟周期,每个时钟周期为20ns,C的初始值为“0”。各操作部件的输出端有直接数据通路连接到有关操作部件的输入端,在操作部件的输出端设置有足够容量的缓冲寄存器。如果处理机内只有一个通用操作部件,采用顺序方式执行指令,那么所需要的时间为(5)。如果单流水线标量处理机,有一条两个功能的静态流水线,流水线每个功能段的延迟时间均为一个时钟周期,加法操作和乘法操作各经过3个功能段,那么所需要的时间为(6)。

A.105.6ms

B.52.8ms

C.39.6ms

D.72.8ms

正确答案:C

-

第2题:

在下列不同结构的处理机上执行6×6的矩阵乘法C=A×B,计算所需要的最短时间。只计算乘法指令和加法指令的执行时间,不计算取操作数、数据传送和程序控制等指令的执行时间。加法部件和乘法部件的延迟时间都是3个时钟周期,另外,加法指令和乘法指令还要经过“取指令”和“指令译码”的时钟周期,每个时钟周期为20ns,C的初始值为“0”。各操作部件的输出端有直接数据通路连接到有关操作部件的输入端,在操作部件的输出端设置有足够容量的缓冲寄存器。如果处理机内只有一个通用操作部件,采用顺序方式执行指令,那么所需要的时间为(25)。如果单流水线标量处理机,有一条两个功能的静态流水线,流水线每个功能段的延迟时间均为一个时钟周期,加法操作和乘法操作各经过3个功能段,那么所需要的时间为(26)。

A.39.6ms

B.72.8ms

C.52.8ms

D.105.6ms

正确答案:A

解析:要完成上面的矩阵乘法,需要完成的各种操作的数量:需要完成的乘法次数为6×6×6=216次。需要完成的加法次数为6×6×5=180次。下面分析处理机的结构会给性能带来什么样的影响。1.顺序执行时,每个乘法和加法指令都需要5个时钟周期(取指令、指令分析、指令执行),所以所需要的时间为:T=(216+180)×5×20ns=39600ns=39.6ms2.单流水线标量处理机,采用两功能静态流水线时,因为有足够的缓冲寄存器,所以可以首先把所有的乘法计算完,并通过调度使加法流水线不出现停顿,所以所需要的时间为:T=T第一条指令进入流水线+T乘法+T加法=[2+(3+216-1)+3(3+180-1).×20ns=8040ns -

第3题:

设有4个作业同时到达,每个作业的执行时间是2min,它们在一台处理机上按单键方式运行,则平均周转时间为 。

B (2+4+6+8)/4=5(小时)。 -

第4题:

某工作站采用时钟频率f为15MHz,处理速率为10MIP/S的处理机来执行一个已知混合程序。假定每次存储器存取为1周期延迟,此计算机的有效CPI是(2),假定将处理机的时钟频率f提高到30MHz,但存储器子系统速率不变。这样,每次存储器存取需要两个时钟周期,如果30%指令每条只需要一次存储存取,而另外5%每条需要两次存储存取,还假定已知混合程序的指令数不变,并与原工作站兼容,则改进后的处理机性能(3)。

A.3

B.1.6

C.0.725

D.1.5

正确答案:D

-

第5题:

主存储器的存储周期和存取时间相同。

B 存取时间(Ta)指从存储器读出或者写入一次信息所需要的平均时间;存取周期(Tc)指连续两次访问存储器之间所必需的最短时间间隔。对Tc一般有:Tc=Ta+Tr,其中Tr为复原时间;对SRAM指存取信息的稳定事件,对DRAM指刷新的又一次存取时间。