半加器与全加器的区别在于半加器无进位输出,而全加器有进位输出。()

题目

半加器与全加器的区别在于半加器无进位输出,而全加器有进位输出。()

相似考题

更多“半加器与全加器的区别在于半加器无进位输出,而全加器有进位输出。()”相关问题

-

第1题:

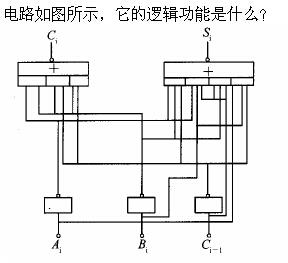

什么叫半加器,什么叫全加器,两者有何不同,半加器可否组成全加器?全加器可否用作半加器?参考答案:半加器是一种不考虑低位来的进位数,只能对本位上的两个二进制数求和的组合电路。全加器是一种将低位来的进位数连同本位的两个二进制数三者一起求和的组合电路。根据化简后的全加器的逻辑式可知,用二个半加器和一个或门可以组合成全加器。将全加器低位进位输入端Ci-1接0,可以用作半加器。

-

第2题:

用()个半加器和最少的门电路可以实现全加器的逻辑功能。A、1

B、2

C、3

D、4

参考答案:B

-

第3题:

全加器比半加器多一根输入线,该输入线是( )。

A.本位进位

B.低位进位

C.加数

D.被加数

正确答案:A

-

第4题:

为什么需要半加器和全加器,它们之间的主要区别是什么?

正确答案: 在做两个进制加法时,右边第一位(最小有效位)相加时要用半加器电路,除此位外,其他各位相加时都要用全加器电路。

全加器的输入端有进位输入,而半加器没有。 -

第5题:

下列不属于组合逻辑电路的加法器为()。

- A、半加器

- B、全加器

- C、多位加法器

- D、计数器

正确答案:D -

第6题:

下列哪组不属于时序逻辑电路()

- A、主从触发器,T触发器

- B、数码寄存器,移位寄存器

- C、异步计数器,同步计数器

- D、半加器,全加器

正确答案:D -

第7题:

下列原件中不属于组合逻辑电路的是()

- A、移位寄存器

- B、半加器

- C、全加器

- D、数据选择器

正确答案:A -

第8题:

能完成两个l位二进制数相加并考虑到低位来的进位的器件称为()。

- A、编码器

- B、译码器

- C、全加器

- D、半加器

正确答案:C -

第9题:

何谓半加器和全加器?

正确答案: 半加器只考虑两个1位二进制数A和B相加,不考虑低进位来的进位数相加称为半加。全加器:除了两个1位二进制数,还与低位向本位的进数相加。 -

第10题:

单选题下列原件中不属于组合逻辑电路的是()A移位寄存器

B半加器

C全加器

D数据选择器

正确答案: A解析: 暂无解析 -

第11题:

单选题只考虑本位数而不考虑低位来的进位的加法称为()。A全加

B半加

C全减

D半减

正确答案: B解析: 暂无解析 -

第12题:

单选题能完成两个l位二进制数相加并考虑到低位来的进位的器件称为()。A编码器

B译码器

C全加器

D半加器

正确答案: D解析: 暂无解析 -

第13题:

既考虑低位进位,又考虑向高位进位,应选应

A、全加器

B、半加器

C、全减器

D、半减器

参考答案:A

-

第14题:

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生向高位的进位Ci以及本位利Si的逻辑电路。(65)和(66)分别是进位和本位和的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(67)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i =1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,CO=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(68)和(69)。

A.XiYi+XiCi-1+YiCi-1

B.XiYi+XiSj+YiSi

C.XiYi+XiCi-1+YiCi-1

D.(XiYi+XiYi).Ci-1

正确答案:C

-

第15题:

A.全加器

A.全加器

B.半加器

C.译码器答案:A解析: -

第16题:

只考虑本位数而不考虑低位来的进位的加法称为()。

- A、全加

- B、半加

- C、全减

- D、半减

正确答案:B -

第17题:

半加器只求()的和。

- A、二进制数

- B、十进制数

- C、本位

- D、来自低位送来的进位

正确答案:C -

第18题:

实现两个一位二进制数和低位进位数相加产生和数及进位数的电路称为半加器。

正确答案:错误 -

第19题:

与4位串行进位加法器比较,使用超前进位全加器的目的是()。

- A、完成自动加法进位

- B、完成4位加法

- C、提高运算速度

- D、完成4位串行加法

正确答案:C -

第20题:

构成一个全加器应由两个半加器和一个()

- A、与非门

- B、与门

- C、或门

- D、或非门

正确答案:C -

第21题:

问答题为什么需要半加器和全加器,它们之间的主要区别是什么?正确答案: 在做两个进制加法时,右边第一位(最小有效位)相加时要用半加器电路,除此位外,其他各位相加时都要用全加器电路。

全加器的输入端有进位输入,而半加器没有。解析: 暂无解析 -

第22题:

单选题构成一个全加器应由两个半加器和一个()A与非门

B与门

C或门

D或非门

正确答案: D解析: 暂无解析 -

第23题:

单选题只考虑本位数而不考虑低位来的进位的器件称为()。A编码器

B译码器

C全加器

D半加器

正确答案: C解析: 暂无解析 -

第24题:

单选题与4位串行进位加法器比较,使用超前进位全加器的目的是()。A完成自动加法进位

B完成4位加法

C提高运算速度

D完成4位串行加法

正确答案: C解析: 暂无解析