某存储器数据总线宽度为32bit,存取周期为250ns,则该存储器带宽为(24)。(注:本题答案中的B表示Byte)A.8×106BpsB.16×106BpsC.16×108BpsD.32×106Bps

题目

某存储器数据总线宽度为32bit,存取周期为250ns,则该存储器带宽为(24)。(注:本题答案中的B表示Byte)

A.8×106Bps

B.16×106Bps

C.16×108Bps

D.32×106Bps

相似考题

参考答案和解析

解析:通常把一条总线所包括的通信线路的数日的多少称为总线带宽。总线带宽通常有8、16、32、64位之分。某存储器数据总线宽度为32bit,存取周期为250ns,则该存储器带宽为:

更多“某存储器数据总线宽度为32bit,存取周期为250ns,则该存储器带宽为(24)。(注:本题答案中的B表示Byte ”相关问题

-

第1题:

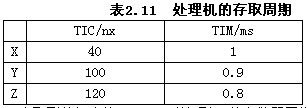

设有三个指令系统相同的处理机X、Y和乙它们都有4KB的高速缓冲存储器和 32 MB的内存,但是其存取周期都不一样,如表2.11所示(TIC和TIM分别表示I处理机 Cahce存取周期和主存存取周期)。

若某段程序所需指令或数据在Cache中取到的概率为P=0.5,则处理机X的存储器平均存取周期为(50)ms。假定指令执行时间与存储器的平均存取周期成正比,此时三个处理机执行该段程序由快到慢的顺序为(51)。

若P=0.65,则顺序为(52)。

若P=0.8,则顺序为(53)。

若P=0.85,则顺序为(54)。

A.0.2

B.0.48

C.0.52

D.0.6

正确答案:C

解析:平均存取周期=Cache存取周期×Cache命中率+主存存取周期×Cache失效率=(0.5×0.04ms+0.5×1ms)=520ns依此类推,因为执行速度与存取周期(执行时间)成反比,因此在Cache命中率分别为0.5、0.65、0.8、0.85的条件下,三个处理机执行该段程序由快到慢的顺序分别为:Z、Y、X,Z、X、Y,X、Z、Y,X、Y、Z。 -

第2题:

如存储器的工作频率为333MHz,数据线宽度为32位,每个周期传输1次数据,则存储器的带宽=___【23】____MB/s。若存储器总线采用串行总线,以10位为一个数据帧(包含一个字节的存储数据),则总线带宽=总线频率/___【24】____。

正确答案:1332 10

-

第3题:

存储器的带宽是指每秒可传输(读出/写入)的最大数据总量。存储器带宽与存储器总线的工作___【19】____有关,也与数据线的___【20】____和每个总线周期的传输次数有关。

正确答案:频率周期 位数位宽

-

第4题:

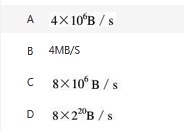

若存储周期为250ns,每次读出16位,则该存储器的数据传送率为(19)。

A.8×106字节/秒

B.4×106字节/秒

C.4M字节/秒

D.8M字节/秒

正确答案:D

解析:本题考查存储器的数据传送率的计算。题目已经告诉我们,存储周期为250ns,即1秒钟可以进行1/250ns次存取操作,而且每次都能读出16位,那么1秒钟总共可以读出的数据为16b×1/250ns÷8=8MB,每次从存储器读出的数据都被传输出去了,因此,存储器的数据传送率为8MB/s。 -

第5题:

计算机的总线包含地址总线、数据总线和控制总线。某计算机CPU有16条地址总线,则该计算机最大的寻址空间为(2)B,若该CPU寻址外部的数据存储器时,第 16条地址线始终为高电平,则此数据存储器的地址空间为(3)B。

A.32K

B.48K

C.64K

D.128K

正确答案:C

-

第6题:

存储器的带宽决定了以存储器为中心的机器获得信息的速度,为了提高存储器带宽,可以采用

A.缩短存取周期

B.增加存储字长

C.增加存储体

D.提高CPU主频

E.增加CPU内总线位数

正确答案:ABC

-

第7题:

在计算机系统中总线宽度分为地址总线宽度和数据总线宽度。若计算机中地址总线的宽度为32位,则最多允许直接访问主存储器(10)的物理空间。A.40MB

B.4GB

C.40GB

D.400GB答案:B解析:本题考查计算机系统基础知识。

在计算机中总线宽度分为地址总线宽度和数据总线宽度。其中,数据总线的宽度(传输线根数)决定了通过它一次所能并行传递的二进制位数。显然,数据总线越宽则每次传递的位数越多,因而,数据总线的宽度决定了在主存储器和CPU之间数据交换的效率。地址总线宽度决定了CPU能够使用多大容量的主存储器,即地址总线宽度决定了CPU能直接访问的内存单元的个数。假定地址总线是32位,则能够访问232=4GB个内存单元。 -

第8题:

若某存储器存储周期为250ns,每次读出16位,则该存储器的数据传输率是()。 答案:C解析:

答案:C解析:

-

第9题:

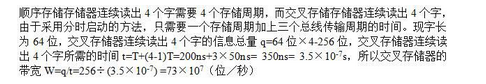

设存储器容量为32位,字长64位,模块数m=8,分别用顺序方式和交叉方式进行组织。若存储周期T = 200ns,数据总线宽度为64位,总线传送周期为50ns,则顺序存储器和交叉存储器带宽各是多少?

略 -

第10题:

系统总线的一个存取周期最快为3个总线时钟周期,在一个总线周期中可以存取32位数据。若总线的时钟频率为8.33MHz,则总线的带宽为多少MB/s?

正确答案: 总线的带宽=数据宽度×总线周期的最高频率=(32/8)Byte×(8.33/3)M/=11.1MB/s -

第11题:

单选题总线宽度为32bit,时钟频率为200MHz,若总线上每5个时钟周期传送一个32bit的字,则该总线的带宽为()MB/SA40

B80

C160

D20

正确答案: C解析: 暂无解析 -

第12题:

填空题如果存储器周期是400ns,而每个周期可访问4字节,则存储器带宽为()。正确答案: 80Mbps解析: 暂无解析 -

第13题:

计算机的总线包含了地址总线,数据总线和控制总线。某计算机CPU有16条地址总线,则该计算机最大的寻址空间为(2)字节,若该CPU寻址外部的数据存储器时,第16条地址线始终为高电平,则此数据存储器的地址空间为(3)字节。

A.32k

B.48k

C.64k

D.128k

正确答案:C

解析:在计算机中,地址线为N条,则最大寻地址空间为2NB。答案为C。 -

第14题:

某总线有104根信号线,其中数据总线(DB)32根。若总线工作频率为33MHz,则其理论最大传输速率为(24)。(注:本题答案中的B表示Byte)

A.33MBps

B.64MBps

C.132MBps

D.164MBps

正确答案:C

解析:总线带宽表示单位时间内总线所能传输的最大数据量。其单位通常用MB/s表示。某总线有104根信号线,其中数据总线(DB)32根。若总线工作频率为33MHz,则其理论最大传输速率R==32×33×106B/s=B/s=132MB/s。 -

第15题:

设某存储器总线的工作频率为100MHz,数据宽度为16位,每个总线周期传输2次,其带宽为___【19】___MB/S,1分钟可传输___【20】___MB数据。

正确答案:400 24000

-

第16题:

总线宽度为 32bit,时钟频率为 200MHz,若总线上每 5 个时钟周期传送一个 32bit 的 字,则该总线的带宽为( )MB/S

A.40

B.80

C.160

D.20

正确答案:C

根据总线时钟频率为200MHz,得1个时钟周期为1/200MHz=0.005μs总线传输周期为0.005μs×5=0.025μs由于总线的宽度为32位=4B(字节)故总线的数据传输率为4B/(0.025μs)=160MBps -

第17题:

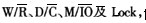

80386有4个总线周期定义信号

但主要的总线周期定义了前三个。在I/O写周期,总线周期定义信号状态为( ),在存储器数据读取周期总线信号定义为( ),在存储器指令码读取周期总线信号定义为( )。

A.

B.

C.

D.

正确答案:ABD

正确答案:ABD

解析:首先需清楚这三个信号的含义,M/信号表示目前被操作的对象是存储器还是I/O,信号为高电平代表是存储器,低电平代表为I/O。信号是区别对所进行的操作对象是数据的存取还是实施控制,高电平代表存取数据,低电平代表控制(包括暂停、中断认可、读取指令码等)。W/R则代表正在进行的操作是写还是读。 -

第18题:

某计算机字长为32位,存储器存取周期为100ns,则存储器的带宽为(10);若CPU执行一段程序,访问存储器1600次,访问cache400次(cache的存储周期为50s),则平均访问存储器的时间为(11)。

(63)

A.32×106bit/s

B.32×107bit/s

C.107bit/s

D.3200bit/s

正确答案:B

-

第19题:

在计算机系统中总线宽度分为地址总线宽度和数据总线宽度。若计算机中地址总线的宽度为32位,则最多允许直接访问主存储器_______物理空间。

A.40MB

B.4GB

C.40GB

D.400GB

答案:B解析:32bit最多能表示的范围就是2^32=4G -

第20题:

设存储器容量为32字,字长64位,模块数m=4,存储周期T=200ns,数据总线宽度为64位,总线传送周期τ=50ns。用交叉方式进行组织,交叉存储器的带宽是()。 答案:C解析:

答案:C解析:

-

第21题:

计算机系统中总线最重要的性能是它的带宽,若总线的数据线宽度为16位,总线的工作频率为133MHZ,每个总线周期传输2次数据,则其带宽为()。

- A、266MB/S

- B、532MB/S

- C、1064MB/S

- D、2128MB/S

正确答案:B -

第22题:

如果存储器周期是400ns,而每个周期可访问4字节,则存储器带宽为()。

正确答案:80Mbps -

第23题:

问答题系统总线的一个存取周期最快为3个总线时钟周期,在一个总线周期中可以存取32位数据。若总线的时钟频率为8.33MHz,则总线的带宽为多少MB/s?正确答案: 总线的带宽=数据宽度×总线周期的最高频率=(32/8)Byte×(8.33/3)M/=11.1MB/s解析: 暂无解析