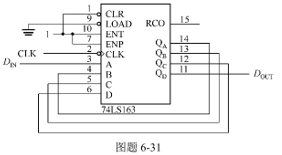

试分析图题6-31所示电路的功能。

题目

试分析图题6-31所示电路的功能。

相似考题

更多“试分析图题6-31所示电路的功能。 ”相关问题

-

第1题:

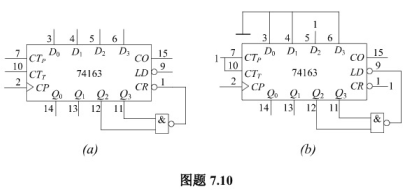

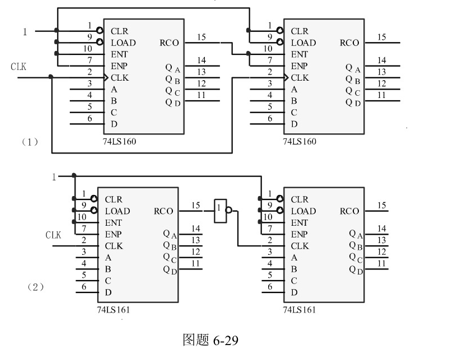

分析图题7.10所示电路,画出它们的状态图和时序图,指出各是几进制计数器。

参考答案:74163 是同步预置、同步清零的16进制同步加法计数器。

参考答案:74163 是同步预置、同步清零的16进制同步加法计数器。

(a) 计数器从0000计数到1100,当为1100时,与非门输出0,在其后的一个CP到来后,计数器变为0000,回到原始初态。于是得出结论,此时为13进制计数器。 (b) 计数器计数到达1100时,与非门输出0,在其后的一个CP到来后,计数器变为0100,回到原始初态。于是得出结论,此时为9进制计数器。

(b) 计数器计数到达1100时,与非门输出0,在其后的一个CP到来后,计数器变为0100,回到原始初态。于是得出结论,此时为9进制计数器。

-

第2题:

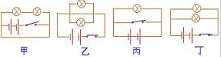

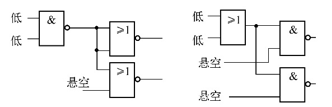

在图所示的四个电路图中,()电路图是正确的。

A.图甲所示的;

B.图乙所示的;

C.图丙所示的;

D.图丁所示的

正确答案:D

-

第3题:

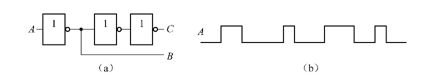

试画出图题2-1 (a) 所示电路在输入图题2-1 (b)波形时的输出端B、C的波形。

图题2-1

答案:

-

第4题:

试确定图题3-26所示74LS门电路的输出负载是灌电流还是拉电流,并确定最大电流值。

图题3-26

答案:(1)输出低电平,因此是灌电流负载,保证输出为0.5V时的最大电流值为8mA。输出高电平,因此是拉电流负载,保证输出为2.7V时的最大电流值为0.4mA。

-

第5题:

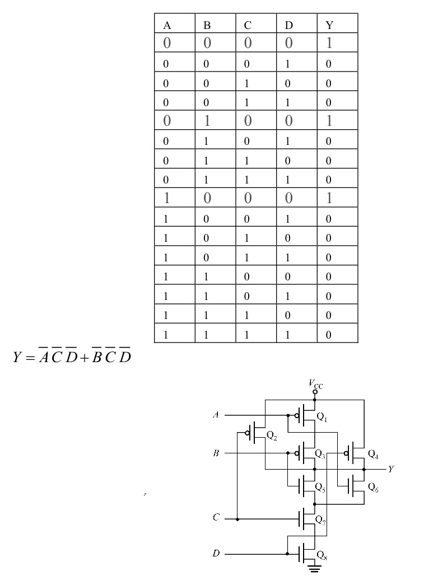

试分析图题3-5所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

答案:

答案:

-

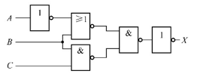

第6题:

图题4-6所示的逻辑电路中,与非门为74LS0O,或非门是74LS02,非门是74LS0试分析该电路的最大传输延迟时间。

图题4-6

答案:74LS00、74LS02和74LS04的最大tpHL和tpLH都是15ns, 因为A信号经过4级门达到输出端X,因此最大传输延迟时间为4×15ns=60ns。

-

第7题:

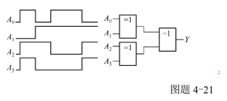

对于图题4-21所示波形作为输入的电路,试画出其输出端的波形。

答案:

答案:

-

第8题:

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第9题:

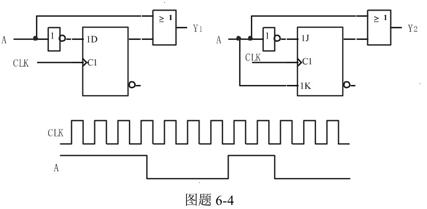

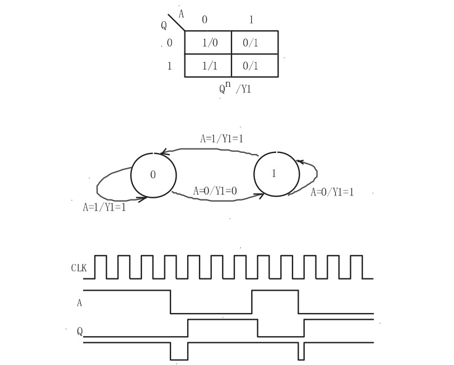

试写出图题6-4所示电路的驱动方程、状态方程、输出方程与状态图,并按

照所给波形画出输出端Y的波形。

答案:左图:

答案:左图:

右图: 由于状态方程=输出方程与左图一样,因此具有与左图相同的状态表、状态图与时序图。

由于状态方程=输出方程与左图一样,因此具有与左图相同的状态表、状态图与时序图。

-

第10题:

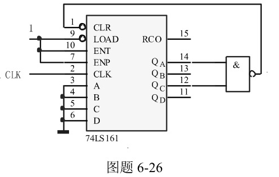

图题6-26所示为具有异步清除功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

答案:异步清零5进制计数器。

答案:异步清零5进制计数器。

-

第11题:

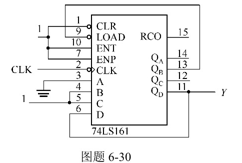

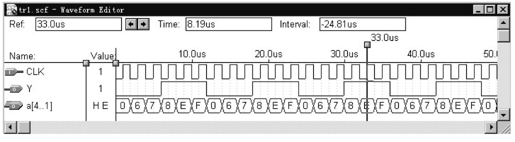

试画出图题6-30所示电路的状态图,并画出时钟CLK作用下的Y端波形。

答案:状态顺序为:6、7、8、E、F、0、6、7、8、E、F写成二进制为: 0000 01100111 1000 1110 1111 0000,因此Y (D)端的波形如下。下图中a..]是计数器输出

答案:状态顺序为:6、7、8、E、F、0、6、7、8、E、F写成二进制为: 0000 01100111 1000 1110 1111 0000,因此Y (D)端的波形如下。下图中a..]是计数器输出

-

第12题:

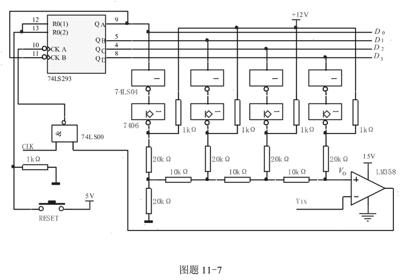

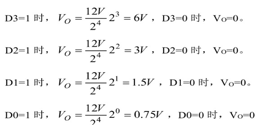

试分析图题11-7所示电路的工作原理。若是输入电压VIN=7.5V,D3~Do是多少?

答案:

答案: 由此可知:输入电压为7.5V,D3~D0=1101,这时Vo=6V+1.5V+0.75V=8.25V,大于输入电压VIn=7.5V,比较器输出低电平,使与非门74LS00封锁时钟脉冲CLK,74LS293停止计数。

由此可知:输入电压为7.5V,D3~D0=1101,这时Vo=6V+1.5V+0.75V=8.25V,大于输入电压VIn=7.5V,比较器输出低电平,使与非门74LS00封锁时钟脉冲CLK,74LS293停止计数。

-

第13题:

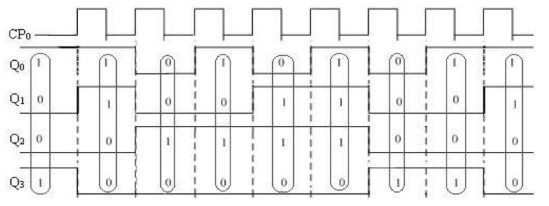

试分析图题7.8的计数器电路,说明这是多少进制的计数器。

参考答案:74160是同步预置、异步清零的8421BCD码10进制同步加法计数器,因此预置只发生在CP脉冲的上升沿。当计数器到达1001后,LD有效,等到CP上升沿到来后,将0011加载给计数器,所以该计数器的状态依次是0011、0100、0101、0110、0111、1000、1001,总共7个状态,所以是7进制计数器。该计数器逻辑波形如下:

参考答案:74160是同步预置、异步清零的8421BCD码10进制同步加法计数器,因此预置只发生在CP脉冲的上升沿。当计数器到达1001后,LD有效,等到CP上升沿到来后,将0011加载给计数器,所以该计数器的状态依次是0011、0100、0101、0110、0111、1000、1001,总共7个状态,所以是7进制计数器。该计数器逻辑波形如下:

-

第14题:

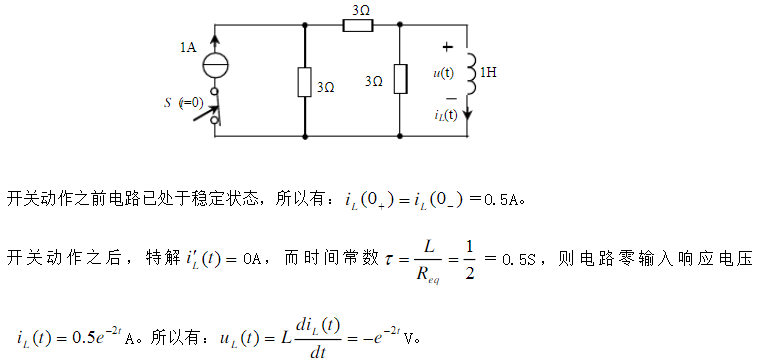

图所示电路开关S在t=0时打开,开关动作之前电路已处于稳定状态,试求电路零输入响应电压u(t)。

参考答案:

参考答案:

-

第15题:

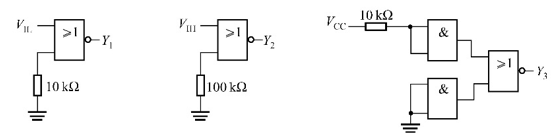

试确定图题 3-25所示74HC门电路的输出状态(设电源Vcc为5 V)。

图题3-25

答案:Y1=高电平; Y2=低电平; Y3=低电平

-

第16题:

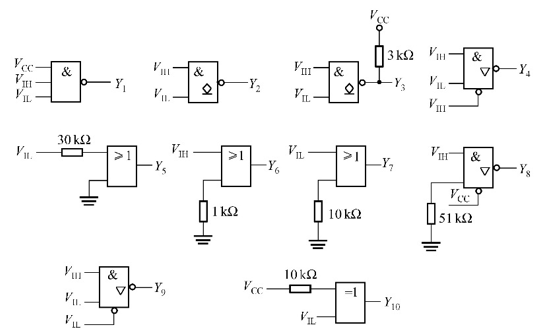

试确定图题3- 24所示74LS门电路的输出状态(设电源Vcc为5V)。

图题3-24

答案:Y1=高电平; Y2= =开路; Y3=高电平; Y4=高阻; Y5=高电平; Y6=高电平Y7=高电平; Y8=高阻; Y9=高电平;Y10=高电平

-

第17题:

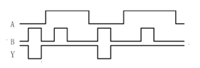

逻辑电路与其输入端的波形如图题4-5所示,试画出逻辑电路输出端Y的波形。

图题4-5

答案:Y=A+B

-

第18题:

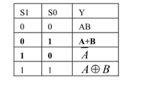

试分析图题4-17所示电路在S、So 信号控制下,其输入A、B与输出Y之间的关系。

答案:由图得到:

答案:由图得到:

-

第19题:

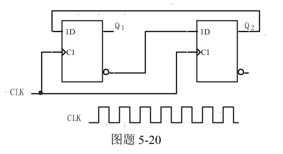

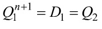

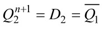

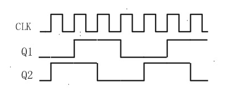

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

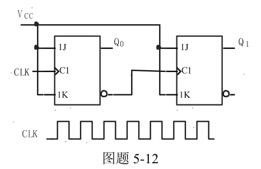

第20题:

试画出图题5-12所示电路输出端Q1、Qo端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第21题:

图题6-25所示为具有同步清除功能的同步四位二进制加法计数器74LS163组成的计数器电路,试说明该计数电路是多少进制。

答案:该电路是异步清零6进制计数器。

答案:该电路是异步清零6进制计数器。

-

第22题:

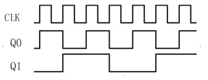

试判断图题6-29所示为电路为多少进制计数器,是同步电路还是异步电路。

答案:上图:同步级连100进制计数器。下图:异步级连100进制计数器。

答案:上图:同步级连100进制计数器。下图:异步级连100进制计数器。

-

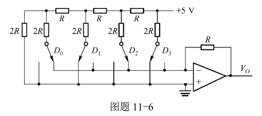

第23题:

试计算图题11-6所示电路的输出电压Vo。

答案:

答案: