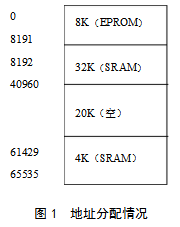

CPU的地址总线16根(A15~A0,A0是低位),双向数据总线16根(D15~D0),控制总线中与主存有关的信号 有!MREQ(允许访存,低电平有效),R/!W(高电平读命令,低电平写命令)。主存地址空间分配如下:0~8191为系统程序区,由EPROM芯片组成,从8192起一共32K地址空间为用户程序区,最后(最大地址)4K地址空间为系统程序工作区。如图1所示。上述地址为十进制,按字编址。现有如下芯片。 EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,

题目

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。相似考题

更多“CPU的地址总线16根(A15~A0,A0是低位),双向数据总线16根(D15~D0),控制总线中与主存有关的信号 有!MREQ(允许访存,低电平有效),R/!W(高电平读命令,低电平写命令)。主存地址空间分配如下:0~8191为系统程序区,由EPROM芯片组成,从8192起一共32K地址空间为用户程序区,最后(最大地址)4K地址空间为系统程序工作区。如图1所示。上述地址为十进制,按字编址。现有如下芯片。<img src="//img.examk.com/exam/o/i/7jzsTL1tyJBvcw81”相关问题

-

第1题:

BHE信号和A0合起来表示当前在总线上出现的从偶地址单元或端口读一个字节的正确序列为:()。A.BHE为低电平,A0为低电平

B.BHE为低电平,A0为高电平

C.BHE为高电平,A0为低电平

D.BHE为高电平,A0为高电平答案:C解析: -

第2题:

地址总线为A15(高位)~A0(低位),若用1K×4的存储芯片组成4K字节存储器,并且以地址总线的高位做片选,则加在各存储芯片上的地址线是()。A.A15~A0

B.A11~A0

C.A9~A0

D.A8~A0答案:C解析:

-

第3题:

设某系统中的数据总线宽度为8bit,地址总线宽度为16bit。若采用4K×4的RAM芯片组成16KB的存储系统。问:设该存储系统从0000H开始占用一段连续地址空间,试给出每组芯片占用的地址范围。

正确答案: 0000~0FFFH

1000~1FFFH

2000~2FFFH

3000~3FFFH -

第4题:

地址总线A0(高位)~A15(低位),用4K×4的存储芯片组成16KB存储器,则加至各存储芯片上的地址线是()。

- A、A16~A15

- B、A0~A9

- C、A0~A11

- D、A4~A15

正确答案:D -

第5题:

某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 该机可以配备的最大主存容量为()。

正确答案:地址总线18位可产生218个选择,数据总线16位,则每个选择输出16位数据。

容量大小为:218×16位=512KB -

第6题:

系统总线中地址总线的功能是()

- A、选择主存地址

- B、选择进行信息传输的设备

- C、选择外存地址

- D、选择主存和I/O设备接口电路的地址

正确答案:D -

第7题:

某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 该机主存采用64K×1位的DRAM芯片(内部为4个128×128阵列)构成最大主存空间,则共需()个芯片;若采用异步刷新方式,单元刷新间隔为2ms,则刷新信号的周期为()。

正确答案:共需(218×16)÷(64K×1bit)=64 芯片;

异步刷新方式是每行刷新一次,则刷新周期是:2ms÷128=15.625μs -

第8题:

MCS—96单片机的最大寻址空间是(),该空间的地址范围为(),系统上电及复位的程序入口地址为(),芯片配置字节CCB的地址为()。

正确答案:64K;0000H—FFFFH;2080H;2018H -

第9题:

问答题某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 该机主存采用64K×1位的DRAM芯片(内部为4个128×128阵列)构成最大主存空间,则共需()个芯片;若采用异步刷新方式,单元刷新间隔为2ms,则刷新信号的周期为()。正确答案: 共需(218×16)÷(64K×1bit)=64 芯片;

异步刷新方式是每行刷新一次,则刷新周期是:2ms÷128=15.625μs解析: 暂无解析 -

第10题:

单选题地址总线A0(高位)~A15(低位),用4K×4的存储芯片组成16KB存储器,则加至各存储芯片上的地址线是()。AA16~A15

BA0~A9

CA0~A11

DA4~A15

正确答案: D解析: 暂无解析 -

第11题:

单选题某型NAND Flash芯片的地址线和数据线是复用的,它具有的部分引脚为ALE、CE、RE、R/B,如果下面每一个选项是用于简述这些引脚的功能的,其中完全正确的是()A低电平有效的芯片使能、命令锁存允许、准备就绪/忙输出、读使能/写使能

B命令锁存允许、低电平有效的写保护、低电平有效的芯片使能、地址锁存允许

C地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出

D准备就绪/忙输出、低电平有效的读使能、低电平有效的写使能、命令锁存允许

正确答案: A解析: NAND Flash主要用于片外程序存储器,为了节省引脚,降低体积,地址线和数据线一般采用分时复用技术。ALE、CE、RE、R/B分别表示地址锁存允许、低电平有效的芯片使能、低电平有效的读使能、准备就绪/忙输出。故C项正确。 -

第12题:

问答题假定某机主存空间大小1GB,按字节编址。cache的数据区(即不包括标记、有效位等存储区)有64KB,块大小为128字节,采用直接映射和全写(write-through)方式。请问: (1)主存地址如何划分?要求说明每个字段的含义、位数和在主存地址中的位置。 (2)cache的总容量为多少位?正确答案: (1)主存空间大小为1GB,按字节编址,说明主存地址为30位。cache共有64KB/128B=512行,因此,行索引(行号)为9位;块大小128字节,说明块内地址为7位。因此,30位主存地址中,高14位为标志(Tag);中间9位为行索引;低7位为块内地址。

(2)因为采用直接映射,所以cache中无需替换算法所需控制位,全写方式下也无需修改(dirty)位,而标志位和有效位总是必须有的,所以,cache总容量为512×(128×8+14+1)=519.5K位。解析: 暂无解析 -

第13题:

在计算机系统中总线宽度分为地址总线宽度和数据总线宽度。若计算机中地址总线的宽度为32位,则最多允许直接访问主存储器_______物理空间。

A.40MB

B.4GB

C.40GB

D.400GB

答案:B解析:32bit最多能表示的范围就是2^32=4G -

第14题:

INTEL 8088 CPU可以访问的存储器空间可达1M,使用的地址信号线为A19~A0,CPU执行一次存储器读操作时,有效控制信号是()。

- A、RD低电平,WR三态,M/IO低电平

- B、RD三态,WR低电平,M/IO高电平

- C、RD低电平,WR高电平,M/IO高电平

- D、RD高电平,WR低电平,M/IO高电平

正确答案:A -

第15题:

假定某机主存空间大小1GB,按字节编址。cache的数据区(即不包括标记、有效位等存储区)有64KB,块大小为128字节,采用直接映射和全写(write-through)方式。请问: (1)主存地址如何划分?要求说明每个字段的含义、位数和在主存地址中的位置。 (2)cache的总容量为多少位?

正确答案: (1)主存空间大小为1GB,按字节编址,说明主存地址为30位。cache共有64KB/128B=512行,因此,行索引(行号)为9位;块大小128字节,说明块内地址为7位。因此,30位主存地址中,高14位为标志(Tag);中间9位为行索引;低7位为块内地址。

(2)因为采用直接映射,所以cache中无需替换算法所需控制位,全写方式下也无需修改(dirty)位,而标志位和有效位总是必须有的,所以,cache总容量为512×(128×8+14+1)=519.5K位。 -

第16题:

地址总线A0(高位)~A15(低位),若用4K×4的存储芯片组成16KB存储器,则应由()译码产生片选信号。

- A、A2A3

- B、A0A1

- C、A12~A15

- D、A0~A5

正确答案:A -

第17题:

地址总线A15(高位)~A0(低位),若用1K×4的存储芯片组成4K字节存储器,则加至各存储芯片上的地址线是()。

- A、A15~A6

- B、A9~A0

- C、A15~A5

- D、A10~A0

正确答案:B -

第18题:

设某系统中的数据总线宽度为8bit,地址总线宽度为16bit。若采用4K×4的RAM芯片组成16KB的存储系统。问:该存储系统至少需要多少根地址总线?其中多少根低位地址线用于片内自选(译码)?

正确答案:至少需要14根地址总线,其中12根低位地址线用于片内自选。 -

第19题:

若地址总线为A15(高位)~A0(低位),若用2KB的存储芯片组成8KB存储器,则加在各存储芯片上的地址线是()。

- A、A11~A0

- B、A10~A0

- C、A9~A0

- D、A8~A0

正确答案:B -

第20题:

单选题总线中的地址总线传输的是( )。[2014年真题]A程序和数据

B主存储器的地址码或外围设备码

C控制信息

D计算机的系统命令

正确答案: D解析:

总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线。根据总线传送信息的类别,可以把总线划分为数据总线、地址总线和控制总线,数据总线用来传送程序或数据;地址总线用来传送主存储器地址码或外围设备码;控制总线用来传送控制信息。 -

第21题:

单选题地址总线A15(高位)~A0(低位),若用1K×4的存储芯片组成4K字节存储器,则加至各存储芯片上的地址线是()。AA15~A6

BA9~A0

CA15~A5

DA10~A0

正确答案: A解析: 暂无解析 -

第22题:

问答题某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 该机可以配备的最大主存容量为()。正确答案: 地址总线18位可产生218个选择,数据总线16位,则每个选择输出16位数据。

容量大小为:218×16位=512KB解析: 暂无解析 -

第23题:

单选题系统总线中地址总线的功能是()A选择主存地址

B选择进行信息传输的设备

C选择外存地址

D选择主存和I/O设备接口电路的地址

正确答案: D解析: 暂无解析