实现两个一位二进制数和来自低位的进位相加的电路叫全加器。对吗?

题目

实现两个一位二进制数和来自低位的进位相加的电路叫全加器。对吗?

相似考题

更多“实现两个一位二进制数和来自低位的进位相加的电路叫全加器。对吗?”相关问题

-

第1题:

既考虑低位进位,又考虑向高位进位,应选应

A、全加器

B、半加器

C、全减器

D、半减器

参考答案:A

-

第2题:

全加器比半加器多一根输入线,该输入线是( )。

A.本位进位

B.低位进位

C.加数

D.被加数

正确答案:A

-

第3题:

试用3线-8线译码器74LS138和门电路实现一位二进制全减器(输入为被减数、减数与来自低位的借位;输出为差和向高位的借位)。要求用按键输入减数、被减数和进位,发光二极管显示减法结果。答案:

-

第4题:

实现两个一位二进制相加产生和数及进位数的电路称为全加器。

正确答案:错误 -

第5题:

能完成两个1位二进制数相加并考虑到低位来的进位的电路称为()。

- A、编码器

- B、译码器

- C、全加器

- D、半加器

正确答案:C -

第6题:

在数字电路中,两个一位二进制数相加叫做()。

- A、半加

- B、3/4加

- C、全加

- D、1/2加

正确答案:A -

第7题:

全加器是一种实现两个一位二进制数以及来自低位的进位相加,产生()及()功能的逻辑电路。

正确答案:和;进位位 -

第8题:

指令“ADDCA,50H”的含义是()

- A、50H中的数与A中的数不带进位位相加

- B、50H中的数与A中的数带进位位相加

- C、50H中的数与A中的数带进位位相减

- D、数50H与A中的数带进位位相加

正确答案:B -

第9题:

能完成两个l位二进制数相加并考虑到低位来的进位的器件称为()。

- A、编码器

- B、译码器

- C、全加器

- D、半加器

正确答案:C -

第10题:

组合逻辑电路中的全加器,输入信号其中有()等。

- A、三个本位输入端

- B、进位端

- C、高位端

- D、低位端

正确答案:B -

第11题:

问答题两个无符号数,它们的大小等于十进制数210和303,用N位二进制存储时,相加产生了进位,用N+1位二进制存储时,相加没有产生进位。这个N等于多少?为什么?正确答案: 210+303=513,29<513<210,取N=9时,相加会产生进位,取N=10,相加就不会产生进位,因此,本题中N=9。解析: 暂无解析 -

第12题:

单选题能完成两个l位二进制数相加并考虑到低位来的进位的器件称为()。A编码器

B译码器

C全加器

D半加器

正确答案: D解析: 暂无解析 -

第13题:

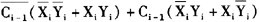

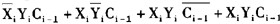

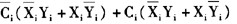

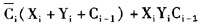

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生向高位的进位Ci以及本位利Si的逻辑电路。(65)和(66)分别是进位和本位和的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(67)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i =1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,CO=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(68)和(69)。

A.XiYi+XiCi-1+YiCi-1

B.XiYi+XiSj+YiSi

C.XiYi+XiCi-1+YiCi-1

D.(XiYi+XiYi).Ci-1

正确答案:C

-

第14题:

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生本位和S,以及向高位的进位Ci的逻辑电路。(51)和(52)分别是Si和Ci的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(53)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i=1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,C0=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(54)和(55)。

A.

B.

C.

D.

正确答案:D

正确答案:D

解析:本位和为1可以分解为:当两加数与低进位均为1的情况(Xi+Yi+Ci-1);当没有进位产生时,两加数、低进位有一个为1的情况Ci(Xi+Yi+Ci-1)。本位进位为1即两加数、低进位同时最少有两个为1的情况,即XiYi+XiCi-1+YiCi-1。半加器异或的作用,Si可表示为两加数、低进位三者若有两个相同,则Si为1,即Xi⊕C⊕i-1Yi。8位加法器中,若C7为0,则符号位由X8.Y8决定,进行异或即可,或表示为x8+y8。若C7为1,则可表示成+x8y8,即C7(+x8y8)+(x8+y8)。若C8=1,表示符号位运算产生进位,此时若C7=0,表示低位没有进位,说明是两加数的符号位运算产生了进位,则结果符号位必然不同于两加数的符号,产生溢出;否则,没有溢出。若C8=0,表示c7,x8,y8,最多有一个是1,若C7=1,说明符号位改变,产生溢出。这种情况可以用半加表示,即C7.C8。 -

第15题:

全加器是指什么?( )A.两个同位的二进制数相加

B.不带进位的两个同位二进制数相加

C.两个同位的二进制数及来自低位的进位三者相加答案:A解析: -

第16题:

半加器只求()的和。

- A、二进制数

- B、十进制数

- C、本位

- D、来自低位送来的进位

正确答案:C -

第17题:

半加器是只求()的和。

- A、二进制数

- B、十进制数

- C、本位

- D、来自低位送来的进位

正确答案:C -

第18题:

实现两个一位二进制数和低位进位数相加产生和数及进位数的电路称为半加器。

正确答案:错误 -

第19题:

两个无符号数,它们的大小等于十进制数210和303,用N位二进制存储时,相加产生了进位,用N+1位二进制存储时,相加没有产生进位。这个N等于多少?为什么?

正确答案: 210+303=513,29<513<210,取N=9时,相加会产生进位,取N=10,相加就不会产生进位,因此,本题中N=9。 -

第20题:

完成两个1位二进制数相加的电路称为()

正确答案:半加器 -

第21题:

全加器是一个只能实现本位两个进制数相加的逻辑电路。

正确答案:错误 -

第22题:

全加器是指两个同位的二进制数及来自低位的进位三者相加。

正确答案:正确 -

第23题:

单选题在数字电路中,两个一位二进制数相加叫做()。A半加

B3/4加

C全加

D1/2加

正确答案: A解析: 暂无解析 -

第24题:

判断题全加器是一个只能实现本位两个进制数相加的逻辑电路。A对

B错

正确答案: 错解析: 暂无解析