单选题若某计算机最复杂指令的执行需要完成5个子功能,分别由功能部件A~E实现,各功能部件所需要时间分别为80ps、50ps、50ps、70ps和50ps,采用流水线方式执行指令,流水段寄存器延时为20ps,则CPU时钟周期至少为( )。A 60psB 70psC 80psD 100ps

题目

60ps

70ps

80ps

100ps

相似考题

参考答案和解析

计算机在一个时钟周期内完成A~E中的一个功能,现在流水段寄存器延时为20ps,则实际上功能部件A~E所需时间依次加20ps,即100ps、70ps、70ps、90ps、70ps。为满足要求CPU的时钟周期至少要大于这5个时间中的最大值,故CPU时钟周期至少为100ps。

更多“单选题若某计算机最复杂指令的执行需要完成5个子功能,分别由功能部件A~E实现,各功能部件所需要时间分别为80ps、50ps、50ps、70ps和50ps,采用流水线方式执行指令,流水段寄存器延时为20ps,则CPU时钟周期至少为( )。A 60psB 70psC 80psD 100ps”相关问题

-

第1题:

设指令由取指、分析、执行3个子部件完成;并且每个子部件的时间均为△t。若采用度为4的超标量流水线处理机,连续执行12条指令,共需花费(4)△t。

A.5

B.9

C.14

D.18

正确答案:A

解析:设指令由取指、分析、执行3个子部件完成;并且每个子部件的时间均为t。①若采用常规标量单流水线处理机(即该处理机的度为1),连续执行12条指令,共需14t。②若采用度为4的超标量流水线处理机,连续执行上述12条指令,只需5t,如图5-7所示。 -

第2题:

设指令由取指、分析和执行3个子部件完成;并且每个子部件的时间均为Δt。若采用度为4的超标量流水线处理机,连续执行12条指令,共需花费(3)Δt。

A.3

B.5

C.9

D.14

正确答案:B

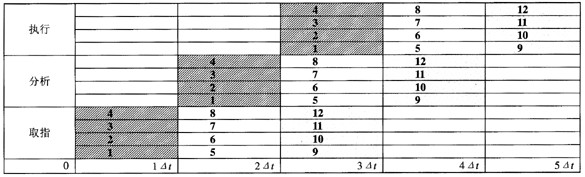

解析:指令由取指、分析和执行3个子部件完成,n=3,且每个子部件的时间均为止Δt。若采用常规标量单流水线处理机(即该处理机的度m=1),连续执行12条(k=-12)指令的时空图如图 2-12所示。执行这12条指令所需的总时间为:Tk=(k+3-1)Δt=(12+3)Δt=14Δt。

若采用度为4(m=4)的超标量流水线处理机,连续执行上述12条(k=12)指令的时空图如图2-13所示。

由图2-`13可知,执行这12条指令所需的总时间只需要5Δt。 -

第3题:

在下列不同结构的处理机上执行6×6的矩阵乘法C=A×B,计算所需要的最短时间。只计算乘法指令和加法指令的执行时间,不计算取操作数、数据传送和程序控制等指令的执行时间。加法部件和乘法部件的延迟时间都是3个时钟周期,另外,加法指令和乘法指令还要经过“取指令”和“指令译码”的时钟周期,每个时钟周期为20ns,C的初始值为“0”。各操作部件的输出端有直接数据通路连接到有关操作部件的输入端,在操作部件的输出端设置有足够容量的缓冲寄存器。如果处理机内只有一个通用操作部件,采用顺序方式执行指令,那么所需要的时间为(25)。如果单流水线标量处理机,有一条两个功能的静态流水线,流水线每个功能段的延迟时间均为一个时钟周期,加法操作和乘法操作各经过3个功能段,那么所需要的时间为(26)。

A.39.6ms

B.72.8ms

C.52.8ms

D.105.6ms

正确答案:A

解析:要完成上面的矩阵乘法,需要完成的各种操作的数量:需要完成的乘法次数为6×6×6=216次。需要完成的加法次数为6×6×5=180次。下面分析处理机的结构会给性能带来什么样的影响。1.顺序执行时,每个乘法和加法指令都需要5个时钟周期(取指令、指令分析、指令执行),所以所需要的时间为:T=(216+180)×5×20ns=39600ns=39.6ms2.单流水线标量处理机,采用两功能静态流水线时,因为有足够的缓冲寄存器,所以可以首先把所有的乘法计算完,并通过调度使加法流水线不出现停顿,所以所需要的时间为:T=T第一条指令进入流水线+T乘法+T加法=[2+(3+216-1)+3(3+180-1).×20ns=8040ns -

第4题:

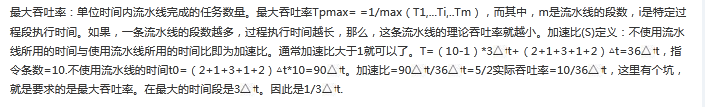

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(4△t)、分析指令( 2△t)、取操作数(6△t)、运算(2△t) , 写回结果(4△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为( ) ;若连续向流水线拉入10条指令,则该流水线的加速比为(请作答此空)。A. 1:10

B. 2:1

C.5:2

D. 3:1答案:C解析:最大吞吐率Tpmax =1/max (T1,... Ti,.. Tm),而其中, m是流水线的段数,是特定过程段执行时间。加速比(S)定义:不使用流水线所用的时间与使用流水线所用的时间比即为加速比。通常加速比大于1。(1) 使用流水线的时间T= (10-1) *6△t+(4+2+6+2+4) △t=72△t,指令条数=10。( 2 )不使用流水线的时间t0= ( 4+2+6+2+4) △t*10=180△t。加速比=90△t/36△t=5/2最大的时间段是3△t.因此最大吞吐率=1/3△t。 -

第5题:

设指令由取指、分析、执行3个子部件完成,每个子部件的工作周期均为△t,采用常规标量流水线处理机。若连续执行10条指令,则共需时间是()。A.8△t

B.10△t

C.12△t

D.14△t答案:C解析:具有3个功能段的流水线连续执行10条指令共需时间=3△t+9△t=12△t。 -

第6题:

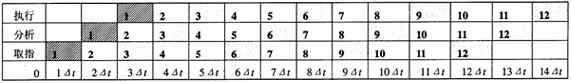

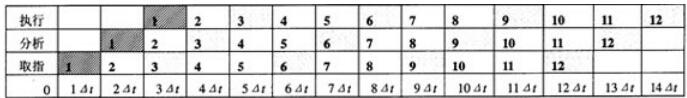

设指令由取指、分析、执行3个子部件完成,并且每个子部件的时间均为△t。若采用常规标量单流水线处理机(即该处理机的度为1),连续执行12条指令,共需(请作答此空)△t。若采用度为4的超标量流水线处理机,连续执行上述12条指令,只需( )△t。A.12

B.14

C.16

D.18答案:B解析:指令由取指、分析和执行3个子部件完成,n=3,且每个子部件的时间均为Δt。若采用常规标量单流水线处理机(即该处理机的度m=1),连续执行12条(k=12)指令的时空图如图所示。执行这12条指令所需的总时间为:Tk=(k+3-1)*Δt=(12+3)*Δt=14Δt。

若采用度为4(m=4)的超标量流水线处理机,连续执行上述12条(k=12)指令的时空图如图所示。

由图可知,执行这12条指令所需的总时间只需要5Δt。 -

第7题:

设指令由取指、分析、执行3个子部件完成,并且每个子部件的时间均为△t。若采用常规标量单流水线处理机(即该处理机的度为1),连续执行12条指令,共需( )△t。若采用度为4的超标量流水线处理机,连续执行上述12条指令,只需(请作答此空)△t。A.3

B.5

C.7

D.9答案:B解析:指令由取指、分析和执行3个子部件完成,n=3,且每个子部件的时间均为Δt。若采用常规标量单流水线处理机(即该处理机的度m=1),连续执行12条(k=12)指令的时空图如图所示。执行这12条指令所需的总时间为:Tk=(k+3-1)*Δt=(12+3)*Δt=14Δt。

若采用度为4(m=4)的超标量流水线处理机,连续执行上述12条(k=12)指令的时空图如图所示。

由图可知,执行这12条指令所需的总时间只需要5Δt。 -

第8题:

某计算机系统采用 5 级流水线结构执行指令,设每条指令的执行由取指令(2 ?t )、分析指令(1?t )、取操作数(3?t )、运算(1?t )和写回结果(2?t ) 组成, 并分别用 5 个子部完成,该流水线的最大吞吐率为() ;若连续向流水线输入 10 条指令,则该流水线的加速比为( 请作答此空) .A. 1:10

B. 2:1

C. 5:2

D. 3:1答案:C解析:本题考察流水线知识,相关计算公式如下:计算机流水线执行周期=最慢那个指令执行时间;流水线执行时间=首条指令执行时间+(指令总数-1)*流水线执行周期;流水线吞吐率=任务数/完成时间;流水线加速比=不采用流水线的执行时间/采用流水线的执行时间;根据公式:流水线执行周期=3?t,流水线执行时间= n/(2?t +1?t +3?t +1?t + 2?t +(n-1)*3?t)=n/[9?t + (n-1)3?t)]=n/(6?t +n*3?t),当n趋向无穷大时,比值为1/3?t10条指令不用流水线的执行时间=(2?t +1?t +3?t +1?t +2?t)*10=90?t。10条指令使用流水线的执行时间=(2?t +1?t +3?t +1?t +2?t)+(10-1)*3?t =36?t。所以加速比为:90?t /36?t =5:2 -

第9题:

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线

正确答案:因为所有组合逻辑块中最长延时为80ps,所以,达到最大可能吞吐率的划分应该是以一个流水段延时为80ps+20ps来进行,因此,至少按五段来划分,分别把流水段寄存器插在A和B、B和C、C和D、D和E之间,这样第一段的组合逻辑延时为80ps,第二段为30ps,第三段为60ps,第四段为50ps,最后一段为70+10=80ps。这样每个流水段都以最长延时调整为80+20=100ps,故时钟周期为100ps,指令吞吐率为1/100ps=10GOPS,每条指令的执行时间为5x100=500ps。 -

第10题:

假定某计算机工程师想设计一个新CPU,一个典型程序的核心模块有一百万条指令,每条指令执行时间为100ps。在非流水线处理器上执行该程序需要花多长时间?

正确答案:非流水线处理器上执行该程序的时间为:100ps×106=100μs. -

第11题:

单选题某CPU主频为1.03GHz,采用4级指令流水线,每个流水段的执行需要1个时钟周期。假定CPU执行了100条指令,在其执行过程中没有发生任何流水线阻塞,此时流水线的吞吐率为( )。A0.25×109条指令/秒

B0.97×109条指令/秒

C1.0×109条指令/秒

D1.03×109条指令/秒

正确答案: D解析:

采用4级指令流水线执行100条指令,在执行过程中共用4+(100-1)=103个时钟周期。CPU的主频是1.03GHz,也就是说每秒钟有1.03G个时钟周期。流水线的吞吐率为1.03G×100/103=1.0×109条指令/秒,故答案为C。 -

第12题:

问答题假定某计算机工程师想设计一个新CPU,一个典型程序的核心模块有一百万条指令,每条指令执行时间为100ps。在非流水线处理器上执行该程序需要花多长时间?正确答案: 非流水线处理器上执行该程序的时间为:100ps×106=100μs.解析: 暂无解析 -

第13题:

下面是有关微处理器指令流水线的叙述,其中错误的是

A.指令流水线中的功能部件(如取指部件、译码部件等)同时执行各自的任务

B.指令流水线在理想情况下,每个时钟都有一条指令执行完毕

C.Pentium处理器中的所谓“超级流水线”就是指级数很多而每级功能又比较简单的流水线

D.Pentium4微处理器中含有三条功能相同的整数运算流水线

正确答案:D

解析:用流水线技术的CPU使用指令重叠的办法,即在一条指令还没有处理完时,就开始处理下一条指令。典型的流水线将每一条机器指令分成取指、译码、取操作数、执行、回写5步。在理想条件下,平均每个时钟周期可以完成一条指令。而所谓“超级流水线处理”是将机器指令划分为更多级的操作,以减轻每一级的复杂程度。在流水线的每一步中,如果需要执行的逻辑操作少一些,则每一步就可以在较短的时间内完成。 -

第14题:

●设每条指令由取指、分析、执行3个子部件完成,并且每个子部件的执行时间均为△t。若采用常规标量单流水线处理机(即该处理机的度为1),连续执行16条指令,则共耗时(14)△t。若采用度为4的超标量流水线处理机,连续执行上述16条指令,则共耗时(15)△t。

(14)A.16

B.18

C.32

D.48

(15) A.4

B.5

C.6

D.8

正确答案:B,C

-

第15题:

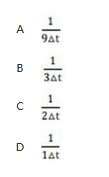

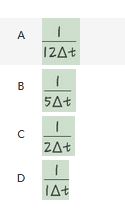

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令( 2△t)、分析指令( 1△t)、取操作数(3△t)、运算(1△t).写回结果 (2△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为(请作答此空) ;若连续向流水线拉入10条指令,则该流水线的加速比为( ) 。 答案:B解析:

答案:B解析:

-

第16题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(3△t)、分析指令(1△t)、取操作数(5△t)、运算(1△t), 写回结果(2△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为( )。 答案:B解析:吞吐率:单位时间内流水线完成的任务数量。

答案:B解析:吞吐率:单位时间内流水线完成的任务数量。

最大吞吐率 =1/max(

),而其中,m是流水线的段数, 是特定过程段执行时间。 -

第17题:

某计算机的指令流水线由四个功能段组成,指令流经各功能段的实际(忽略功能段之间的缓存时间)分别是90ns,80ns,70ns,60ns,则该CPU时钟周期至少是()。A.60ns

B.70ns

C.80ns

D.90ns答案:D解析:时钟周期应以最长的执行时间为准,否则用时长的流水段功能将不能正确完成。 -

第18题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(2 Δt )、分析指令(1Δt )、取操作数(3Δt )、运算(1Δt )和写回结果(2Δt ) 组成, 并分别用5 个子部件完成,该流水线的执行周期为(请作答此空) ;若连续向流水线输入10条指令,该流水线完成的时间为( )。A.3Δt

B.1Δt

C.2Δt

D.7Δt答案:A解析:流水线的执行周期为流水线执行时间最长的一段。10条指令使用流水线的执行时间=(2Δt+1Δt+3Δt+1Δt+2Δt)+(10-1)*3Δt=36Δt。 -

第19题:

某计算机系统采用4级流水线结构执行命令,设每条指令的执行由取指令(2Δt)、分析指令(1Δt)、取操作数(3Δt)、运算并保存结果(2Δt)组成(注:括号中是指令执行周期)。并分别用4个子部件完成,该流水线的最大吞吐率为(请作答此空);若连续向流水线输入5条指令,则该流水线的加速比为( )。A.1

B.1/2Δt

C.1/3Δt

D.1/8Δt答案:C解析:流水线的最大吞吐率为指令执行周期的倒数,流水线的加速比是不使用流水线的执行时间与使用流水线的执行时间的比值,题干中不使用流水线的执行时间=(2Δt+1Δt+3Δt+2Δt)*5=40Δt,使用流水线的执行时间=(2Δt+1Δt+3Δt+2Δt)+3Δt*(5-1)=20Δt,流水线的加速比为2:1。 -

第20题:

某计算机的指令流水线由四个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90ns、80ns、70ns和60ns,则该计算机的CPU时钟周期至少是()。

- A、90ns

- B、80ns

- C、70ns

- D、60ns

正确答案:A -

第21题:

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?插入三个流水段寄存器,得到一个四级流水线

正确答案:三个流水段寄存器分别插在A和B、C和D、D和E之间,这样第一个流水段的组合逻辑延时为80ps,第二段时延为30+60=90ps,第三段时延为50ps,最后一段延时为70+10=80ps。这样每个流水段都以最长延时调整为90+20=110ps,故时钟周期为110ps,指令吞吐率为1/110ps=9.09GOPS,每条指令的执行时间为4x110=440ps。 -

第22题:

单选题某计算机的指令流水线由四个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90ns、80ns、70ns和60ns,则该计算机的CPU时钟周期至少是()。A90ns

B80ns

C70ns

D60ns

正确答案: A解析: 暂无解析 -

第23题:

问答题假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线正确答案: 因为所有组合逻辑块中最长延时为80ps,所以,达到最大可能吞吐率的划分应该是以一个流水段延时为80ps+20ps来进行,因此,至少按五段来划分,分别把流水段寄存器插在A和B、B和C、C和D、D和E之间,这样第一段的组合逻辑延时为80ps,第二段为30ps,第三段为60ps,第四段为50ps,最后一段为70+10=80ps。这样每个流水段都以最长延时调整为80+20=100ps,故时钟周期为100ps,指令吞吐率为1/100ps=10GOPS,每条指令的执行时间为5x100=500ps。解析: 暂无解析