由或非门构成的基本SR锁存器,当S=0,R=1时,锁存器输出状态为__________。

题目

由或非门构成的基本SR锁存器,当S=0,R=1时,锁存器输出状态为__________。

相似考题

更多“由或非门构成的基本SR锁存器,当S=0,R=1时,锁存器输出状态为__________。”相关问题

-

第1题:

输出端子的接通/断开状态,由输出锁存器决定。()

参考答案:√

-

第2题:

数字量输入通道主要由()、输入调理电路、输入地址译码等组成。

A、输入缓冲器

B、输入锁存器

C、输出缓冲器

D、输出锁存器

参考答案:A

-

第3题:

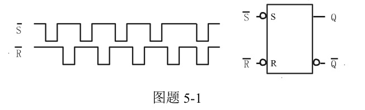

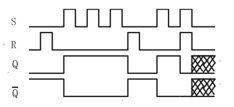

画出图题5-1所示的SR锁存器输出端Q、端的波形,输入端与的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第4题:

8086在最小模式下,分时使用AD0-AD15,所以必须外接地址锁存器,当总线上为地址信息时,通过()将地址送入地址锁存器。

- A、DEN

- B、ALE

- C、BHE

- D、DT/R

正确答案:B -

第5题:

8255A工作于基本输入/输出方式下,输出和输入数据()。

- A、输出数据锁存,输入数据不锁存

- B、输出数据锁存,输入数据锁存

- C、输出数据不锁存,输入数据锁存

- D、输出数据不锁存,输入数据不锁存

正确答案:A -

第6题:

8253—5每个计数内部都有()。

- A、8位控制寄存器、16位计数初值寄存器CR、计数执行部件CE、输出锁存器OL

- B、8位状态寄存器,8位控制寄存器,8位计数初值寄存器CR、计数执行部件CE、输出锁存器OL

- C、16位计数初值寄存器CR、计数执行部件CE、输出锁存器OL

- D、16位计数初值寄存器CR、计数执行部件CE、控制寄存器

正确答案:C -

第7题:

Intel 8255AB端口有一个()。

- A、8位数据输入锁存器和8位数据输出缓冲器

- B、8位数据输入缓冲器和8位数据输出缓冲要

- C、8位数据输入缓冲器和 8位数据输出锁存/缓冲器

- D、8位数据输入锁存器和8位数据锁存器

正确答案:C -

第8题:

由两个TTL或非门构成的基本RS触发器,当R=S=0时,触发器的状态为不定。

正确答案:错误 -

第9题:

输出锁存器的状态,由当前输出刷新期间输出映像寄存器的状态决定。

正确答案:错误 -

第10题:

单选题Intel 8255A A端口有一个()。A8位数据输入锁存器和8位数据输出锁存/缓冲器

B8位数据输入缓冲器和8位数据输出缓冲器

C8位数据输入锁存器与8位数据输出缓冲器

D8位数据输入缓冲器和8位数据输出缓冲/锁存器

正确答案: A解析: 暂无解析 -

第11题:

单选题Intel 8255AC端口有一个()。A8位数据输入锁存器和8位数据输出缓冲器

B8位数据输入缓冲器和8位数据输出缓冲要

C8位数据输入缓冲器和 8位数据输出锁存/缓冲器

D8位数据输入锁存器和8位数据锁存器

正确答案: B解析: 暂无解析 -

第12题:

单选题8255A工作于基本输入/输出方式下,输出和输入数据()。A输出数据锁存,输入数据不锁存

B输出数据锁存,输入数据锁存

C输出数据不锁存,输入数据锁存

D输出数据不锁存,输入数据不锁存

正确答案: A解析: 暂无解析 -

第13题:

由两个TTL或非门构成的基本RS触发器,当R=S=0时,触发器的状态为不定。()此题为判断题(对,错)。

参考答案:错

-

第14题:

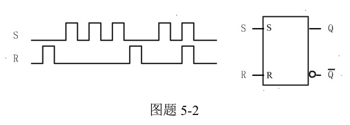

画出图题5-2所示的SR锁存器输出端Q、Q—端的波形,输入端S与R的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第15题:

在I/O接口电路中,输出数据必通过锁存器,输入数据必须通过()。

- A、锁存器

- B、缓冲器

- C、译码器

- D、控制器

正确答案:B -

第16题:

什么是地址锁存器?8086/8088系统中为什么要用地址锁存器?锁存的是什么信息?

正确答案:地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数据和地址总线采用分时复用操作方法,即用同一总线既传输数据又传输地址。当微处理器与存储器交换信号时,首先由CPU发出存储器地址,同时发出允许锁存信号ALE给锁存器,当锁存器接到该信号后将地址/数据总线上的地址锁存在总线上,随后才能传输数据。 -

第17题:

Intel 8255A A端口有一个()。

- A、8位数据输入锁存器和8位数据输出锁存/缓冲器

- B、8位数据输入缓冲器和8位数据输出缓冲器

- C、8位数据输入锁存器与8位数据输出缓冲器

- D、8位数据输入缓冲器和8位数据输出缓冲/锁存器

正确答案:A -

第18题:

输出锁存器有何作用?

正确答案:计数输出锁存器OL用来锁存计数执行部件CE的内容,从而使微处理器可以对此进行读操作。 -

第19题:

用作单片机地址锁存器的芯片一般有()等。

- A、16D触发器

- B、8D触发器

- C、32位锁存器

- D、16位锁存器

- E、8位锁存器

正确答案:B,E -

第20题:

已知R、S是或非门构成的基本RS触发器的输入端,则约束条件为()。

- A、RS=0

- B、R+S=I

- C、RS=l

- D、R+S=0

正确答案:A -

第21题:

或非门构成的基本RS触发器,S端为0,R端为1,这时RS触发器状态为:1。

正确答案:错误 -

第22题:

单选题对8255接口电路写一个控制命令字使其工作于方式0时,则()。A输入、输出均有锁存功能

B输出有锁存功能,输入不锁存

C输入有锁存功能,输出不锁存

D输出、输入均不锁

正确答案: A解析: 暂无解析 -

第23题:

判断题基本输出接口是保持微处理器输出数据的一个锁存器。A对

B错

正确答案: 对解析: -

第24题:

单选题接口电路74LS373的控制端11和1的状态分别为0、0,该373是处在()。A高阻抗状态

B输入锁存状态

C输入直接输出

D输出已锁存的数据

正确答案: B解析: 暂无解析