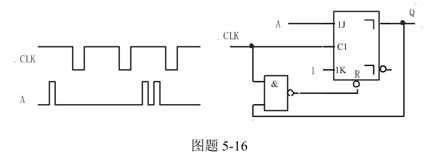

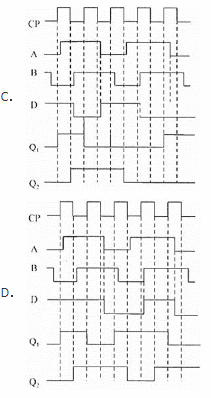

图(a)所示时序逻辑电路的工作波形如图(b)所示,由此可知,图(a)电路是一个( )。 A.右移寄存器 B.三进制计数器 C.四进制计数器 D.五进制计数器

题目

B.三进制计数器

C.四进制计数器

D.五进制计数器

相似考题

更多“图(a)所示时序逻辑电路的工作波形如图(b)所示,由此可知,图(a)电路是一个( )。 ”相关问题

-

第1题:

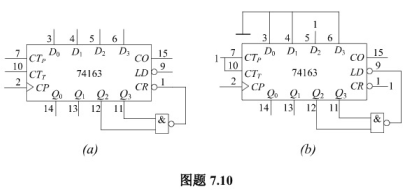

分析图题7.10所示电路,画出它们的状态图和时序图,指出各是几进制计数器。

参考答案:74163 是同步预置、同步清零的16进制同步加法计数器。

参考答案:74163 是同步预置、同步清零的16进制同步加法计数器。

(a) 计数器从0000计数到1100,当为1100时,与非门输出0,在其后的一个CP到来后,计数器变为0000,回到原始初态。于是得出结论,此时为13进制计数器。 (b) 计数器计数到达1100时,与非门输出0,在其后的一个CP到来后,计数器变为0100,回到原始初态。于是得出结论,此时为9进制计数器。

(b) 计数器计数到达1100时,与非门输出0,在其后的一个CP到来后,计数器变为0100,回到原始初态。于是得出结论,此时为9进制计数器。

-

第2题:

为用ARM芯片的一根GPIO引脚驱动一个LED(发光二极管),设计了如下图(a)~(d)共4个具体的电路。图中,设计得最合理的电路是:()。

A.(a)图所示的电路

B.(b)图所示的电路

C.(c)图所示的电路

D.(d)图所示的电路

正确答案:A

-

第3题:

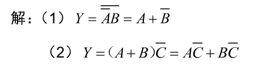

写出图题2-23所示逻辑电路的逻辑函数式。

答案:

答案:

-

第4题:

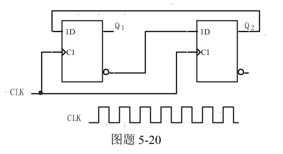

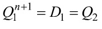

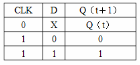

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第5题:

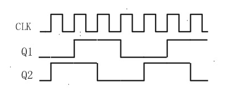

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第6题:

图(a)所示时序逻辑电路的工作波形如图(b)所示,由此可知,图(a)电路是一个( )。 A.右移寄存器

A.右移寄存器

B.三进制计数器

C.四进制计数器

D.五进制计数器答案:C解析:根据题96图(b)可知,时序电路的输出状态为:000—001—010—100—000—100……。因此,时序电路为四进制计数器。 -

第7题:

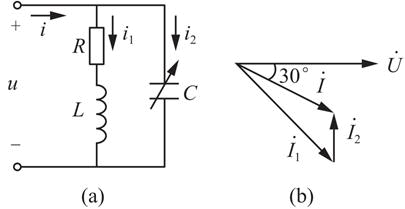

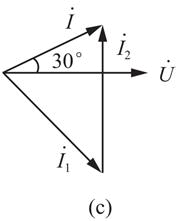

图(a)所示功率因数补偿电路中,C=C1时得到相量图如图(b)所示,C=C2时得到相量图如图(c)所示,那么( )。

答案:D解析:

答案:D解析:

-

第8题:

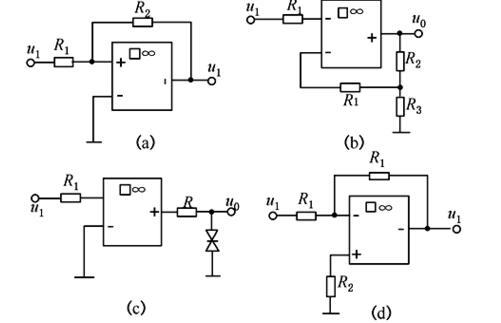

如图所示电路中,符合u+=u-≈0(即虚地)的电路是( )。 A.图(a)

A.图(a)

B.图(b)

C.图(c)

D.图(d)答案:D解析:虚短的必要条件是运放引入深度负反馈。图(d)中引入了深度负反馈,且运算放大器的一个输入端通过电阻接地,未接其他信号,符合“虚地”的条件;其他图不能满足上述条件。 -

第9题:

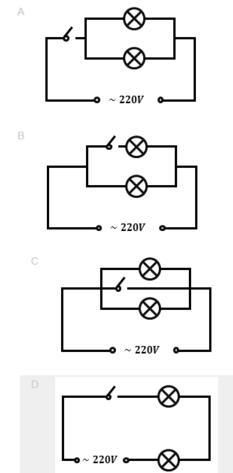

用一个开关控制办公室里的两盏灯,最合理的电路图是( )。 A. 如图所示,选A

A. 如图所示,选A

B. 如图所示,选B

C. 如图所示,选C

D. 如图所示,选D答案:A解析:并联保证灯泡的电压相等,并联灯泡之间互相不受影响 -

第10题:

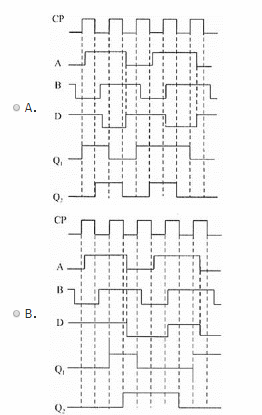

逻辑电路图及相应的输入CP、A、B的波形分别如图所示,初始状态Q1=Q2=0,当RD=1时,D、Q1、Q2端输出的波形分别是( )。

答案:A解析:首先分析D端输出,D的逻辑表达式为

答案:A解析:首先分析D端输出,D的逻辑表达式为

故只有当A=B=1时,D=0,可排除B、D项。D触发器为边沿触发器,特征表如题28解表所示,输出Q只在时钟信号边沿改变,分析可得,A、C选项的Q1端输出均为正确的。对于第二个JK触发器,它的时钟信号与CP相反,当Q1=1时,输出Q2在每个时钟信号的下降沿翻转;当Q1=0时,输出Q2在时钟信号的下降沿变为0,可得A项正确。

-

第11题:

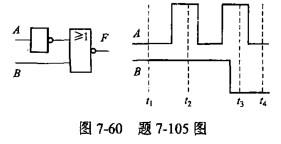

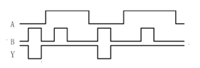

逻辑电路和输入A、B的时序波形如图7-60所示,当输出F为高电平的时刻是( )。

A.t1 B.t2 C.t3 D.t4答案:C解析:正确答案是C。

-

第12题:

在时序逻辑电路分析过程中所画的l工作波形就是:()

- A、真值表

- B、时序图

- C、状态转移图

- D、电路图

正确答案:B -

第13题:

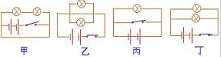

在图所示的四个电路图中,()电路图是正确的。

A.图甲所示的;

B.图乙所示的;

C.图丙所示的;

D.图丁所示的

正确答案:D

-

第14题:

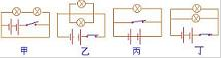

如图所示的四个电路图中,电源的电压均为U,每个电阻的阻值都为R1,()图中安培表的示数最大。

A.图甲所示的;

B.图乙所示的;

C.图丙所示的;

D.图丁所示的

正确答案:C

-

第15题:

逻辑电路与其输入端的波形如图题4-5所示,试画出逻辑电路输出端Y的波形。

图题4-5

答案:Y=A+B

-

第16题:

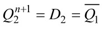

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第17题:

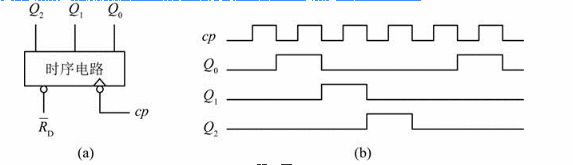

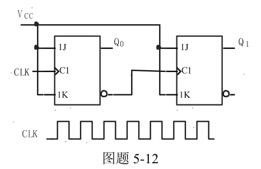

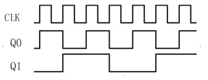

试画出图题5-12所示电路输出端Q1、Qo端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第18题:

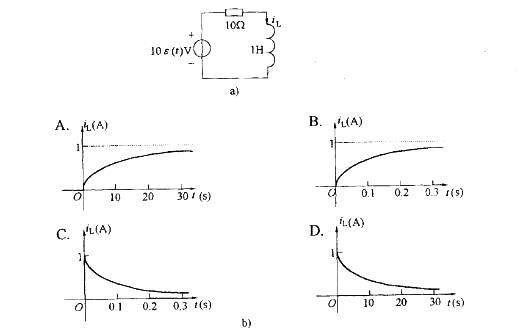

电路如图a)所示,iL(t)的波形为图b)中的哪个图所示? 答案:B解析:

答案:B解析: -

第19题:

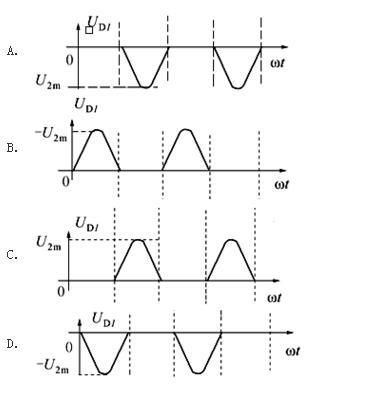

单相桥式整流电路如图a)所示,变压器副边电压U2的波形如图b)所示,设4个二极管均为理想元件,则二极管D1两端的电压uD1的波形是图c)中哪个图所示?

答案:B解析:

答案:B解析: -

第20题:

单相桥式整流电路如图图(a)所示,变压器副边电压u2的波形如图(b)所示,设四个二极管均为理想元件,则二极管D1两端的电压uD1的波形为图(c)中的( )图。

答案:B解析:在变压器副边电压的正半周,二极管D和D导通,D和D截止;在电压的副半周时,二极管D1和D3导通,D2和D4截止。二极管D1截至时,两端的电压uD1为一个半波电压;导通时,理想二极管相当于短路,两端电压为零。

答案:B解析:在变压器副边电压的正半周,二极管D和D导通,D和D截止;在电压的副半周时,二极管D1和D3导通,D2和D4截止。二极管D1截至时,两端的电压uD1为一个半波电压;导通时,理想二极管相当于短路,两端电压为零。 -

第21题:

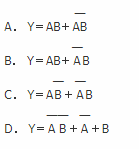

图所示波形是某种组合电路的输入、输出波形,该电路的逻辑表达式为( )。

答案:C解析:根据波形图,列真值表如题25解表:

答案:C解析:根据波形图,列真值表如题25解表:

-

第22题:

如图b)所示电源与图a)所示电路等效,则计算Us和R0的正确算式为:

答案:C解析:提示 根据戴维南定理,图b)中的电压源U's为图a)的开路电压,电阻R0的数值为图a)的除源电阻。

答案:C解析:提示 根据戴维南定理,图b)中的电压源U's为图a)的开路电压,电阻R0的数值为图a)的除源电阻。

-

第23题:

时序逻辑电路的()都可以用来描述同一个时序电路的逻辑功能,所以它们之间可以互相转换。

- A、状态转换表

- B、状态转换图

- C、时序图

- D、卡诺图

正确答案:A,B,C -

第24题:

分析时序逻辑电路的步骤为:() ①根据给定的时序逻辑电路,写出存储电路输入信号的逻辑函数表达式。 ②写出状态转移方程。 ③列出状态转移表或画出状态转移图。 ④画出工作波形。

- A、①②③④

- B、①③④②

- C、②③④①

- D、①②④③

正确答案:A