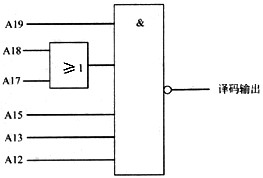

如下图所示,若低位地址(/AO~A11)接在内存芯片地址引脚上,高位地址(A12~ A19)进行片选译码(其中,A14和A16没有参加译码),且片选信号低电平有效,则对下图所示的译码器,不属于此译码空间的地址为(36)。A.AB000H~ABFFFHB.BB000H~BBFFFHC.EF000H~EFFFFHD.FE000H~FEFFFH

题目

如下图所示,若低位地址(/AO~A11)接在内存芯片地址引脚上,高位地址(A12~ A19)进行片选译码(其中,A14和A16没有参加译码),且片选信号低电平有效,则对下图所示的译码器,不属于此译码空间的地址为(36)。

A.AB000H~ABFFFH

B.BB000H~BBFFFH

C.EF000H~EFFFFH

D.FE000H~FEFFFH

相似考题

更多“如下图所示,若低位地址(/AO~A11)接在内存芯片地址引脚上,高位地址(A12~ A19)进行片选译码(其中,A14和A16没有参加译码),且片选信号低电平有效,则对下图所示的译码器,不属于此译码空间的地址为(36)。A.AB000H~ABFFFHB.BB000H~BBFFFHC.EF000H~EFFFFHD.FE000H~FEFFFH”相关问题

-

第1题:

在现行PC机中,常用存储器地址线中的低10位作输入/输出口地址线。设某接口芯片内部有16个端口,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为( )。

A.全部10位地址线

B.其中的高8位地址线

C.其中的高6位地址线

D.其中的高4位地址线

正确答案:C

-

第2题:

● 如下图所示,若低位地址(A0-A11)接在内存芯片地址引脚上,高位地址(A12-A19)进行片选译码(其中,A14 和 A16 没有参加译码) ,且片选信号低电平有效,则对下图所示的译码器,不属于此译码空间的地址为 (36) 。

(36)

A. AB000H~ABFFFH

B. BB000H~BBFFFH

C. EF000H~EFFFFH

D. FE000H~FEFFFH

正确答案:D

-

第3题:

【问题1】(5分)

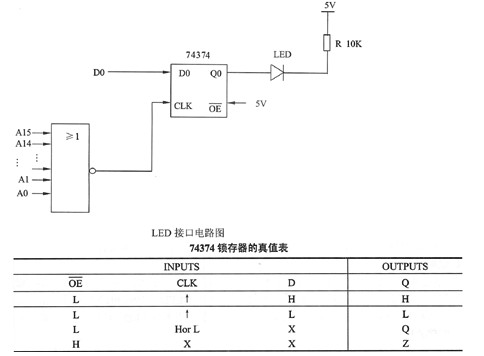

图2-1所示的LED接口电路中有设计错误,请找出其中至少4处错误(从编号为①~⑧的备选答案中选择)。

①74374的

接5V

接5V②A16~A19没参加接口地址译码

③LED的限流电阻R的阻值太小

④译码器为或非门

⑤LED阴极接电源

⑥/MEMW没参加接口地址译码

⑦/IOW没参加接口地址译码

⑧LED的限流电阻R的阻值太大

正确答案:

本题的解答与次序无关,只要选对均可给分。①74374的接5V④译码器为或非门⑤LED阴极接电源⑦/IOW没参加接口地址译码⑧LED的限流电阻R的阻值太大考生只答编号亦可;考生答出其中的4项或5项给5分;答错一个扣1分(到0分为止);若考生将题目中的8个选项全部列出则不给分。 -

第4题:

有一微机系统,采用CPU的低10位地址线A0~A9作为输入输出口的地址线,系统中接口芯片内部有16个端口地址,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为()。A.A5~A9

B.A4~A9

C.A2~A9

D.A0~A9答案:B解析: -

第5题:

存储器与CPU进行连接时,如果使用了译码器,则译码器的输出应接到存储器的:()

- A、数据线

- B、地址线

- C、写选通

- D、片选

正确答案:D -

第6题:

地址总线A0(高位)~A15(低位),若用4K×4的存储芯片组成16KB存储器,则应由()译码产生片选信号。

- A、A2A3

- B、A0A1

- C、A12~A15

- D、A0~A5

正确答案:A -

第7题:

在8088处理器系统中,假设地址总线A19~A15输出01011时译码电路产生一个有效的片选信号。这个片选信号将占有主存从()到()的物理地址范围,共有()容量。

正确答案:58000H;5FFFFH;32KB -

第8题:

下述产生片选信号CS#的方法中,被选中的芯片不具有唯一确定地址的是()。

- A、线选法或部分译码

- B、仅部分译码

- C、仅线选法

- D、全译码

正确答案:A -

第9题:

一般用空余的()输出一些控制信号形成片选信号。只有片选信号有效时,才能对所连芯片的存储单元进行读写。

- A、普通地址译码

- B、低位地址译码

- C、高位地址译码

- D、特殊地址译码

正确答案:C -

第10题:

单选题接口电路中的译码器是对CPU的哪种信号译码产生片选信号?()A数据信号

B地址信号

C控制信号

D数据信号和控制信号

正确答案: D解析: 暂无解析 -

第11题:

单选题在存储器连线时,线片控制采用()方式时,不存在()的问题,即所分配的地址是连续的。A全译码地址重叠

B线选控制地址浮动

C线选控制地址重叠

D全译码地址浮动

正确答案: C解析: -

第12题:

填空题对一个存储器芯片进行片选译码时,有一个高位系统地址信号没有参加译码,则该芯片的每个存储单元占有()个存储器地址。正确答案: 2解析: 暂无解析 -

第13题:

阅读以下关于LED接口电路的叙述,回答问题1至问题2,将答案填入答题纸的对应栏内。

[说明]

某计算机系统采用内存和接口统一编址方式。内存可寻址空间为1MB,内存地址用 A0~A19传送,读写信号分别为/MEMR和/MEMW;接口可寻址空间为64KB,接口地址用A0~A15传送,读写信号分别为/IOR和/IOW。

在该计算机系统上设计的LED接口电路如下图所示,分配的接口地址为0000H。图中的74374为锁存器,其真值表见下表。

Z表示高阻。

上图所示的LED接口电路中有设计错误,请找出其中至少4处错误(从编号为①~⑧的备选答案中选择)。

①74374的

接5V

接5V②A16~A19没参加接口地址译码

③LED的限流电阻R的阻值太小

④译码器为或非门

⑤LED阴极接电源

⑥/MEMW没参加接口地址译码

⑦/IOW没参加接口地址译码

⑧LED的限流电阻R的阻值太大

正确答案:①74374的 接5V

④译码器为或非门

⑤LED阴极接电源

⑦/IOW没参加接口地址译码

⑧LED的限流电阻R的阻值太大

接5V

④译码器为或非门

⑤LED阴极接电源

⑦/IOW没参加接口地址译码

⑧LED的限流电阻R的阻值太大

①74374的 接5V

④译码器为或非门

⑤LED阴极接电源

⑦/IOW没参加接口地址译码

⑧LED的限流电阻R的阻值太大 解析:①图中设计“74374的

接5V

④译码器为或非门

⑤LED阴极接电源

⑦/IOW没参加接口地址译码

⑧LED的限流电阻R的阻值太大 解析:①图中设计“74374的 接5V”的做法是错误的。因为74374是具有三态输出的 D触发器,其三态输出的允许信号

接5V”的做法是错误的。因为74374是具有三态输出的 D触发器,其三态输出的允许信号 应该接地,如果

应该接地,如果 接5V,使得74374输出高阻。

接5V,使得74374输出高阻。

②图中“A16~A19没参加接口地址译码”的描述是正确的。因为根据题意,要求的是接口寻址,接口地址用A0~A15传送,故A16~A19不参加接口地址译码。

③从图中可以看出,LED的限流电阻R的阻值太大,应该减小。

④图中设计的译码器采用的是或非门,这种设计是不正确的。因为根据题意分配的接口地址为0000H,所以译码器采用或门才能符合设计要求。

⑤图中设计“LED阴极接电源”的做法是错误的。LED阴极应接地,并将电阻减小;或者将LED阴极接到QO端,并将电阻减小。

⑥/MEMR和/MEMW是内存读写信号,读写接口时不需要用到。

⑦图中设计的“/IOW”没参加接口地址译码的做法是错误的。

⑧图中设计的“LED的限流电阻R的阻值太大”的做法是错误的。 -

第14题:

在现行PC机中,常用存储器地址线中的低10位作输入输出口地址线。设某接口芯片内部有16个端口,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为( )。

A.其中的高8位地址线

B.其中的高4位地址线,

C.其中的高6位地址线

D.以上都不对

正确答案:C

-

第15题:

74138译码器通常用于产生片选信号,其译码输入端应与系统的()总线相连。A.地址

B.数据

C.控制

D.串行

参考答案:A

-

第16题:

有一微机系统,采用CPU的低10位地址线A0~A9作为输入输出口的地址线,系统中接口芯片内部有16个端口地址,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为()。

- A、A5~A9

- B、A4~A9

- C、A2~A9

- D、A0~A9

正确答案:B -

第17题:

74138译码器通常用于产生片选信号,其译码输入端应与系统的()总线相连。

- A、地址

- B、数据

- C、控制

- D、串行

正确答案:A -

第18题:

设某系统有20条地址线,现欲以4K×1b的RAM芯片构成64KB的存储系统,试问:需要()片这样的芯片。用全译码方式进行地址译码,参与片外译码的地址线是()条。

正确答案:128;4 -

第19题:

对一个存储器芯片进行片选译码时,有一个高位系统地址信号没有参加译码,则该芯片的每个存储单元占有()个存储器地址。

正确答案:2 -

第20题:

接口电路中的译码器是对CPU的哪种信号译码产生片选信号?()

- A、数据信号

- B、地址信号

- C、控制信号

- D、数据信号和控制信号

正确答案:B -

第21题:

在全译码中,利用系统的某一条地址线作为芯片的片选信号。

正确答案:错误 -

第22题:

填空题在8088处理器系统中,假设地址总线A19~A15输出01011时译码电路产生一个有效的片选信号。这个片选信号将占有主存从()到()的物理地址范围,共有()容量。正确答案: 58000H,5FFFFH,32KB解析: 暂无解析 -

第23题:

单选题74138译码器通常用于产生片选信号,其译码输入端应与系统的()总线相连。A地址

B数据

C控制

D串行

正确答案: C解析: 暂无解析