下列关于Cache的描述中,哪一个是错误的?(17)。A.Cache是缓冲技术在存储体系中的一个具体应用B.Cache的主要特点之一是存储容量大C.Cache处于内存和CPU之间D.Cache中一般存放内存的一部分副本

题目

下列关于Cache的描述中,哪一个是错误的?(17)。

A.Cache是缓冲技术在存储体系中的一个具体应用

B.Cache的主要特点之一是存储容量大

C.Cache处于内存和CPU之间

D.Cache中一般存放内存的一部分副本

相似考题

参考答案和解析

解析:Cache处于内存和CPU之间,负责解决主存与CPU之间速度的协调问题。它跟内存相比主要特点是:存取速度快,存储量小。

更多“下列关于Cache的描述中,哪一个是错误的?(17)。A.Cache是缓冲技术在存储体系中的一个具体应用B.Cac ”相关问题

-

第1题:

● 下面关于计算机Cache的论述中,正确的是 (3) 。

(3)A.Cache是一种介于主存和辅存之间的存储器,用于主辅存之间的缓冲存储

B.如果访问 Cache 不命中,则用从内存中取到的字节代替Cache 中最近访问 过的字节

C.Cache的命中率必须很高,一般要达到90%以上

D.Cache中的信息必须与主存中的信息时刻保持一致

正确答案:C

-

第2题:

下面关于CPU与 Cache 之间关系的叙述中,正确的是

A.Cache中存放的是主存储器中一部分信息的映像

B.用户可以直接访问Cache

C.片内Cache要比二级Cache的容量大得多

D.二级Cache要比片内Cache的速度快得多

正确答案:A

-

第3题:

下列关于Cache的描述中,哪一个是错误的?

A.Cache是缓冲技术在存储体系中的一个具体应用

B.Cache的主要特点之一是存储容量大

C.Cache处于内存和CPU之间

D.Cache中一般存放内存的一部分副本

正确答案:B

-

第4题:

下面是关于CPU与主存储器之间的cache的叙述,其中正确的是:( )。

A.cache中存放的只是主存储器中某一部分内容的映像

B.cache能由用户直接访问

C.位于主板上的L2cache要比与CPU封装在一起的L2cache速度快

D.位于主板上的L2cache要比与CPU做在一个基片上的L2cache速度快

正确答案:A

解析:目前在PC系统中一般设有一级缓存(L1cache)和二级缓存(L2cache),二级缓存以前一般做在主板上,速度等于CPU的外频,也有将第二级缓存同CPU封装在一起的,其速度为CPU主频的一半或与CPU主频相等。cache不能有用户直接访问。 -

第5题:

以下关于CPU与主存之问增加高速缓存(Cache)的叙述中,错误的是______。

A.Cache扩充了主存储器的容量

B.Cache可以降低由于CPU与主存之间的速度差异造成的系统性能影响

C.Cache的有效性是利用了对主存储器访问的局部性特征

D.Cache中通常保存着主存储器中部分内容的一份副本

A.

B.

C.

D.

正确答案:A

解析:本题考查计算机系统基础知识。

Cache(高速缓冲存储器)是一种特殊的存储器子系统,其中复制了频繁使用的数据以利于快速访问。Cache的出现是基于两种原因:首先是由于CPU的速度和性能提高很快而主存速度较低且价格高,其次就是程序执行的局部性特点。因此,将速度比较快而容量有限的SRAM构成Cache,目的在于尽可能发挥CPU的高速度。 -

第6题:

以下关于CPU与主存之间增加高速缓存(Cache)的叙述中,错误的是______。

A.Cache扩充了主存储器的容量

B.Cache可以降低由于CPU与主存之间的速度差异造成的系统性能影响

C.Cache的有效性是利用了对主存储器访问的局部性特征

D.Cache中通常保存着主存储器中部分内容的一份副本

正确答案:A

解析:本题考查计算机系统基础知识。

Cache(高速缓冲存储器)是一种特殊的存储器子系统,其中复制了频繁使用的数据以利于快速访问。Cache的出现是基于两种因素:首先,是由于CPU的速度和性能提高很快而主存速度较低且价格高,第二就是程序执行的局部性特点。因此,才将速度比较快而容量有限的SRAM构成Cache,目的在于尽可能发挥CPU的高速度。 -

第7题:

在下列因素中,与Cache的命中率无关的是_______。

A.Cache块的大小

B.Cache的容量

C.主存的存取时间

正确答案:C

-

第8题:

下面是关于CPU与主存储器之间的Cache的叙述,其中正确的是( )。

A.Cache中存放的主存储器中某一部分内容的映象

B.Cache能由用户直接访问

C.位于主板上的12 Cache要比与CPU封装在一起的L1 Cache速度快

D.Cache存储器的功能不全由硬件实现

正确答案:A

-

第9题:

在计算机系统中,以下关于高速缓存 (Cache) 的说法正确的是( )。

A.Cache的容量通常大于主存的存储容量B.通常由程序员设置Cache的内容和访问速度C.Cache 的内容是主存内容的副本D.多级Cache 仅在多核cpu中使用

正确答案:C

-

第10题:

● 下面关于 Cache(高速缓冲存储器)的叙述, “ (9) ”是错误的。

(9)

A. 在体系结构上,Cache 存储器位于主存与 CPU之间

B. Cache 存储器存储的内容是主存部分内容的拷贝

C. 使用 Cache 存储器并不能扩大主存的容量

D. Cache 的命中率只与其容量相关

正确答案:D

-

第11题:

以下关于cache的叙述中,正确的有( )。A.cache和主存都用半导体芯片作为存储介质,因此它们的存取速度相差不大

B.在程序中不能用数据传送指令cache中某个单元中存储的内容

C.cache存储容量的大小对计算机的运行速度会产生影响

D.只有将一个程序的全部指令从内存装入cache才能在CPU中运行该程序答案:B,C解析:高速缓冲存储(cache),比主存储器体积小但速度快,用于保存从主存储器得到指令的副本的专用缓冲器。高速缓冲存储器是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多。接近于CPU的速度.并且其容量的大小影响计算机运行速度。故本题正确选项是BC。 -

第12题:

下面是对高速缓冲存储器(CAChe)的描述,正确的有()

- A、CAChe是位于CPU与主存储器之间,对用户是透明的一种高速小容量存储器

- B、在现代CPU设计技术中,常将CAChe分成一级CAChe和二级CAChe

- C、一级CAChe容量一般较小,二级CAChe的容量相对一级CAChe要大一些

- D、高速缓存中存放的是正在运行的一小段程序和数据

正确答案:A,B,C,D -

第13题:

以下关于Cache(高速缓冲存储器)的描述,(9)是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

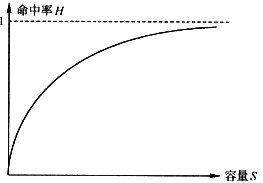

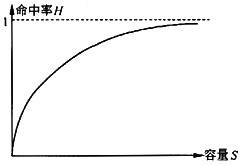

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对 Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况;当发生Cache块失效时,所采用的替换算法;Cache的容量;在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等。Cache的命中率随其容量增加而提高,它们之间的关系曲线如下图所示。在Cache容量比较小的时候,命中率提高的非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这实际上是做不到的。

-

第14题:

在Cache-主存两级存储体系中,关于Cache的叙述,错误的是(15)。

A.Cache设计的主要目标是在成本允许的情况下达到较高的命中率,使存储系统具有最短的平均访问时间

B.Cache设计的一个重要原则是在争取获得较快的存取速度和花费较低的存储成本之间达到合理的折衷

C.除了Cache容量和块的大小,地址相联方式和替换策略也会影响Cache的命中率

D.在速度要求较高的场合采用直接映像,在速度要求较低的场合采用组相联或全相联

正确答案:D

解析:本题考查高速缓存的相关知识。

为解决高速CPU与低速内存之间的速度差异,最经济、有效的方法是在两者之间插入容量不大但操作速度很高的存储器高速缓存(Cache),起到缓冲作用,使CPU既可以以较快速度存取Cache中的数据,又不使系统成本过高。

与主存相比,Cache的容量很小,它保存的只是一部分主存内容的一个副本,且Cache与主存的数据交换是以块为单位。

地址映射即是应用某种方法把主存地址定位到Cache中,有全相联方式、直接方式和组相联方式三种方式。

(1)全相联映射方式。

这是一种最简单而又直接的映射方法,指主存中每个块只能映射到Cache的一个特定的块。在该方法中,Cache块地址j和主存块地址i的关系为:

j=imodCb

其中Cb是Cache的块数。这样,整个Cache地址与主存地址的低位部分完全相同。

直接映射法的优点是所需硬件简单,只需要容量较小的按地址访问的区号标志表存储器和少量比较电路;缺点是Cache块冲突概率较高,只要有两个或两个以上经常使用的块恰好被映射到Cache中的同一个块位置时,就会使Cache命中率急剧下降。

(2)直接映射方式。

这种映射方式允许主存的每一块信息可以存到Cache的任何一个块空间,也允许从已被占满的Cache中替换掉任何一块信息。全相联映射的优点是块冲突概率低:其缺点是访问速度慢,并且成本太高。

(3)组相联映射方式。

这种方式是前两种方式的折衷方案。这种映射方式在组间是直接映射,而组内是全相联映射,其性能和复杂性介于直接映射和全相联映射之间。

CPU在访问内存时,首先判断所要访问的内容是否在Cache中,如果在,就称为“命中”,此时CPU直接从Cache中调用该内容;否则,就称为“不命中”。一般来说,Cache的存储容量比主存的容量小得多,但不能太小,太小会使命中率太低;也没有必要过大,过大不仅会增加成本,而且当容量超过一定值后,命中率随容量的增加将不会有明显地增长。 -

第15题:

Pentium内部有两个独立的8KB的超高速缓冲存储器,一个是8KB的代码Cache,另一个是8KB的【 】。

正确答案:数据Cache

数据Cache 解析:Pentium内部有两个独立的8KB的超高速缓冲存储器,即8KB的代码Cache和8KB的数据Cache。其中一个只保存指令,另一个只保存数据。 -

第16题:

关于存储器读写速度,下列排序正确的是( )。

A.Cache>RAM>硬盘>软盘

B.RAM>Cache>硬盘>软盘

C.Cache>硬盘>RAM>软盘

D.RAM>Cache>软盘>硬盘

正确答案:A

解析:关于存储器读写速度,正确的是Cache>RAM>硬盘>软盘。 -

第17题:

关于Cache(高速缓冲存储器)的说法中,错误的是(9)。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对 Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况:当发生Cache块失效时,所采用的替换算法:Cache的容量:在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等。Cache的命中率随它的容量的增加而提高,它们之间的关系曲线见下图所示。在 Cache容量比较小的时候,命中率的提高得非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这实际上是做不到的。

-

第18题:

在Cache-主存两级存储体系中,关于Cache的叙述,错误的是(11)。

A.Cache设计的主要目标是在成本允许的情况下达到较高的命中率,使存储系统具有最短的平均访问时间

B.Cache设计的一个重要原则是在争取获得较快的存取速度和花费较低的存储成本之间达到合理的折衷

C.除了Cache容量和块的大小,地址相联方式和替换策略也会影响Cache的命中率

D.在速度要求较高的场合采用直接映像,在速度要求较低的场合采用组相联或全相联 试题11分析

正确答案:D

本题考查高速缓存的相关知识。为解决高速CPU与低速内存之间的速度差异,最经济、有效的方法是在两者之间插入容量不大但操作速度很高的存储器高速缓存(Cache),起到缓冲作用,使CPU既可以以较快速度存取Cache中的数据,又不使系统成本过高。与主存相比,Cache的容量很小,它保存的只是一部分主存内容的一个副本,且Cache与主存的数据交换是以块为单位。地址映射即是应用某种方法把主存地址定位到Cache中,有全相联方式、直接方式和组相联方式三种方式。(1)全相联映射方式。这是一种最简单而又直接的映射方法,指主存中每个块只能映射到Cache的一个特定的块。在该方法中,Cache块地址j和主存块地址i的关系为:j=imodCb其中Cb是Cache的块数。这样,整个Cache地址与主存地址的低位部分完全相同。直接映射法的优点是所需硬件简单,只需要容量较小的按地址访问的区号标志表存储器和少量比较电路;缺点是Cache块冲突概率较高,只要有两个或两个以上经常使用的块恰好被映射到Cache中的同一个块位置时,就会使Cache命中率急剧下降。(2)直接映射方式。这种映射方式允许主存的每一块信息可以存到Cache的任何一个块空间,也允许从已被占满的Cache中替换掉任何一块信息。全相联映射的优点是块冲突概率低:其缺点是访问速度慢,并且成本太高。(3)组相联映射方式。这种方式是前两种方式的折衷方案。这种映射方式在组间是直接映射,而组内是全相联映射,其性能和复杂性介于直接映射和全相联映射之间。CPU在访问内存时,首先判断所要访问的内容是否在Cache中,如果在,就称为“命中”,此时CPU直接从Cache中调用该内容;否则,就称为“不命中”。一般来说,Cache的存储容量比主存的容量小得多,但不能太小,太小会使命中率太低;也没有必要过大,过大不仅会增加成本,而且当容量超过一定值后,命中率随容量的增加将不会有明显地增长。 -

第19题:

下面是关于CPU与主存储器之间的cache的叙述,其中正确的是( )。

A.cache中存放的只是主存储器中部分内容的映像

B.cache的工作方式可以根据需要由软件进行设置

C.cache与主存储器是两个各自独立的存储部件,可以选择使用其中的一个

D.cache通常是由DRAM制作的

正确答案:A

解析:cache中存放的只是主存储器中部分内容的映像,其他三种说法均不正确。 -

第20题:

常用的虚拟存储寻址系统由( )两级存储器组成。

A.Cache—Cache

B.Cache—主存

C.Cache—外存

D.主存—外存

正确答案:D

-

第21题:

关于计算机中的存储体系,下面的论述中,正确的是(15)。

A.Cache是一种介于主存和辅存之间的存储器,用于主/辅存之间的缓冲存储

B.如果防问Cache不命中,则用从内存中取到的字代替Cache中最近访问过的字

C.Cache的命中率必须很高,一般要达到90%以上

D.Cache中的信息必须与主存中的信息时刻保持一致

正确答案:C

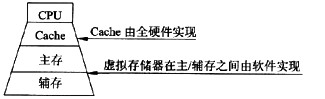

解析:Cache是介于CPU和主存之间的存储器,虚拟存储器是介于主存和辅存之间的存储器,三者之间的关系如下图所示,Cache用全硬件实现,虚拟存储器在主存和辅存之间用软件实现。

Cache的命中率必须很高,一般要达到90%以上,才能使访存的速度跟得上CPU的速度。在CPU和Cache之间通常一次传送一个字块,字块的长度是一个主存周期内能调出的信息的长度。如果访问Cache不命中,则从主存中取出需要的字块,同时送CPU和 Cache,下次就可以从Cache中读出需要的信息了。如果程序执行过程中要对某字块进行写操作,这时就遇到如何保持Cache与主存一致性的问题。通常有两种写入方式:一种是只写Cache,并用标志加以说明,直到经过重写的字块被从Cache中替换出来时再写入主存,叫做“写回法”:另外一种方法是写Cache时也同时写入主存,使Cache与主有时刻保持一致,称之为“直写法”。然而如果被重写的单元不在Cache中,那就只写入主存,而不写入Cache。可见不是所有的情况下都可以保持Cache中的信息与主存中的信息完全一致。 -

第22题:

以下关于Cache(高速缓冲存储器)的叙述中,不正确的是( )。A.Cache的设置扩大了主存的容量

B.Cache的内容是主存部分内容的拷贝

C.Cache的命中率并不随其容量增大线性地提高

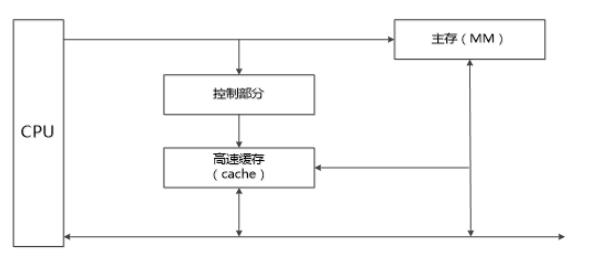

D.Cache位于主存与CPU之间答案:A解析:高速缓存是用来存放当前最活跃的程序和数据的,作为主存局部域的副本,其特点是:容量一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器构成;其内容是主存局部域的副本,对程序员来说是透明的。高速缓存的组成如下图所示:Cache由两部分组成:控制部分和cache部分。Cache部分用来存放主存的部分拷贝(副本)信息。控制部分的功能是:判断CPU要访问的信息是否在cache中,若在即为命中,若不在则没有命中。命中时直接对cache存储器寻址。未命中时,要按照替换原则,决定主存的一块信息放到cache的哪一块里面。

-

第23题:

以下关于计算机系统中高速缓存(Cache)的说法中,正确的是( )。A.Cache的容量通常大于主存的存储容量

B.通常由程序员设置Cache的内容和访问速度

C.Cache的内容是主存内容的副本

D.多级Cache仅在多核CPU中使用答案:C解析:高速缓冲存储器是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多,接近于CPU的速度。Cache通常保存着一份内存储器中部分内容的副本(拷贝),该内容副本是最近曾被CPU使用过的数据和程序代码。