使用 Cache 改善系统性能的依据是程序的局部性原理。程序中大部分指令是(60)的。设某计算机主存的读/写时间为 100ns,有一个指令和数据合一的 Cache,已知该 Cache的读/写时间为 10ns,取指令的命中率为 98%,取数的命中率为 95%。在执行某类程序时,约有 1/5 指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置 Cache 后,每条指令的平均读取时间约为(61)ns。A.顺序存储、顺序执行 B.随机存储、顺序执行 C.顺序存储、随机执行 D.随机存储、随机执

题目

B.随机存储、顺序执行

C.顺序存储、随机执行

D.随机存储、随机执行

相似考题

更多“使用 Cache 改善系统性能的依据是程序的局部性原理。程序中大部分指令是(60)的。设某计算机主存的读/写时间为 100ns,有一个指令和数据合一的 Cache,已知该 Cache的读/写时间为 10ns,取指令的命中率为 98%,取数的命中率为 95%。在执行某类程序时,约有 1/5 指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置 Cache 后,每条指令的平均读取时”相关问题

-

第1题:

在多级存储系统中,Cache处在CPU和主存之间,解决(55)问题。若Cache和主存的存取时间分别为T1和T2,Cache的命中率为H,则该计算机实际存取时间为(56)。当CPU向存储器执行读操作时,首先访问Cache,若命中,则从Cache中取出指令或数据,否则从主存中取出,送(57):当CPU向存储器执行写操作时,为了使Cache的内容和主存的内容保持一致,若采用(58)法,则同时写入Cache和主存。由于Cache容量比主存容量小,因此当Cache满时,执行把主存信息向Cache写入,就要淘汰Cache中已有的信息,为了提高Cache的命中率,采用一种(59)替换算法。

A.主存容量扩充

B.主存和CPU速度匹配

C.多个请求源访问主存

D.BIOS存放

正确答案:B

解析:he的主要功能是提供CPU与RAM间的速度匹配问题,存储器效率的计算公式为:HTI+(1-H)T2。为了提高Cache的命中率,我们常采用LRU最近最少使用的替换算法。 -

第2题:

若Cache和主存的存取时间分别为T1和T2,Cache的命中率为H,则该计算机的实际存取时间为(2)。当CPU向存储器执行读操作时,首先访问Cache,如命中,则从Cache中取出指令或数据,否则从主存中取出,送(3);当CPU向存储器执行写操作时,为了使Cache内容和主有的内容保持一致,若采用(4)法,同时写入Cache和主存。

A.H×T1+T2

B.(1-H×T1)+H×T2

C.T2-H×T1

D.H×T1+(1-H)×T2

正确答案:D

解析:Cache的命中率为H,则访问内存概率为1-H,因此实际存取时间为H×T1+(1-H)×T2。 -

第3题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令( 2△t)、分析指令( 10t)、取操作数(3△t)、运算(1Ot), 写回结果(20t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为( ) ; 若连续向流水线拉入10条指令,则该流水线的加速比为(请作答此空)。A.1:10

B.2:1

C.5:2

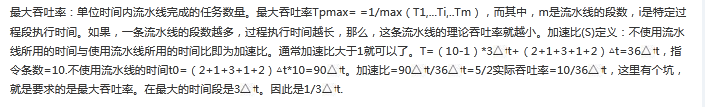

D.3:1答案:C解析:最大吞吐率:单位时间内流水线完成的任务数量。最大吞吐率Tpmax= =1/max (..j..m , 而其中, m是流水线的段数,是特定过

程段执行时间。如果,-条流水线的段数越多 ,过程执行时间越长,那么,这条流水线的理论吞吐率就越小。加速比(S)定义:不使用流水

线所用的时间与使用流水线所用的时间比即为加速比。通常加速比大于1就可以了。T= (10-1) *3△t+ (2+1+3+1+2) st=36△t,指

令条数=10.不使用流水线的时间t0= ( 2+1+3+1+2) 4t*10=90△t。加速比=90△t/36△t= 5/2实际吞吐率=10/36△t,这里有个坑,

就是要求的是最大吞吐率。在最大的时间段是3△t。因此是1/3△t -

第4题:

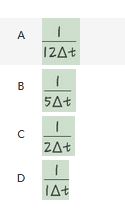

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(4△t)、分析指令( 2△t)、取操作数(6△t)、运算(2△t), 写回结果(4△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为(请作答此空) ;若连续向流水线拉入10条指令,则该流水线的加速比为( )。 答案:B解析:最大吞吐率Tpmax =1/max (Tr,. Ti,.. Tm),而其中, m是流水线的段数,是特定过程段执行时间。加速比(S)定义:不使用

答案:B解析:最大吞吐率Tpmax =1/max (Tr,. Ti,.. Tm),而其中, m是流水线的段数,是特定过程段执行时间。加速比(S)定义:不使用

流水线所用的时间与使用流水线所用的时间比即为加速比。通常加速比大于1。( 1 )使用流水线的时间T= ( 10-1) *6△t+(4+2+6+2+4) △t=72△t,指令条数=10。( 2 )不使用流水线的时间t0= ( 4+2+6+2+4) △t*10=180△t。加速比=90△t/36△t=5/2最大的时间段是3△t,因此最大吞吐率=1/3△t. -

第5题:

在Cache和主存构成的两级存储体系中,主存与Cache同时访问,Cache的存取时间是100ns,主存的存取时间是1000ns,如果希望有效(平均)存取时间不超过Cache存取时间的115%,则Cache的命中率至少应为()。A.90%

B.98%

C.95%

D.99%答案:D解析:设命中率为x,则可得到100x+1000(1-x)≤100×(1+15%),简单计算后可得结果为x≥98.33%,因此命中率至少为99%。 -

第6题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(2 Δt )、分析指令(1Δt )、取操作数(3Δt )、运算(1Δt )和写回结果(2Δt ) 组成, 并分别用5 个子部件完成,该流水线的执行周期为( ) ;若连续向流水线输入10条指令,该流水线完成的时间为(请作答此空)。A.46Δt

B.36Δt

C.90Δt

D.40Δt答案:B解析:流水线的执行周期为流水线执行时间最长的一段。10条指令使用流水线的执行时间=(2Δt+1Δt+3Δt+1Δt+2Δt)+(10-1)*3Δt=36Δt。 -

第7题:

使用 Cache 改善系统性能的依据是程序的局部性原理。程序中大部分指令是(请作答此空)的。设某计算机主存的读/写时间为 100ns,有一个指令和数据合一的 Cache,已知该 Cache的读/写时间为 10ns,取指令的命中率为 98%,取数的命中率为 95%。在执行某类程序时,约有 1/5 指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置 Cache 后,每条指令的平均读取时间约为( )ns。A.12.3

B.14.7

C.23.4

D.26.3答案:B解析:(100*2%+10*98%)+(100*5%+10*95%)*20%=14.7 -

第8题:

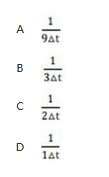

某计算机系统采用 5 级流水线结构执行指令,设每条指令的执行由取指令(2 ?t )、分析指令(1?t )、取操作数(3?t )、运算(1?t )和写回结果(2?t ) 组成, 并分别用 5 个子部完成,该流水线的最大吞吐率为(请作答此空 ) ;若连续向流水线输入 10 条指令,则该流水线的加速比为() .A. 1/9?t

B. 1/3 ?t

C. 1/2?t

D. 1/1?t答案:B解析:本题考察流水线知识,相关计算公式如下:计算机流水线执行周期=最慢那个指令执行时间;流水线执行时间=首条指令执行时间+(指令总数-1)*流水线执行周期;流水线吞吐率=任务数/完成时间;流水线加速比=不采用流水线的执行时间/采用流水线的执行时间;根据公式:流水线执行周期=3?t,流水线执行时间= n/(2?t +1?t +3?t +1?t + 2?t +(n-1)*3?t)=n/[9?t + (n-1)3?t)]=n/(6?t +n*3?t),当n趋向无穷大时,比值为1/3?t10条指令不用流水线的执行时间=(2?t +1?t +3?t +1?t +2?t)*10=90?t。10条指令使用流水线的执行时间=(2?t +1?t +3?t +1?t +2?t)+(10-1)*3?t =36?t。所以加速比为:90?t /36?t =5:2 -

第9题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(2Δt)、分析指令(1Δt)、取操作数(3Δt)、运算(1Δt)和写回结果(2Δt)组成,并分别用5个子部完成,该流水线的最大吞吐率为()A.. 1/9Δt

B. 1/3Δt

C. 1/2Δt

D. 1/1Δt答案:B解析:本题考察流水线知识,相关计算公式如下:计算机流水线执行周期=最慢那个指令执行时间;流水线执行时间=首条指令执行时间+(指令总数-1)*流水线执行周期;流水线吞吐率=任务数/完成时间;流水线加速比=不采用流水线的执行时间/采用流水线的执行时间;根据公式:流水线执行周期=3Δt,流水线执行时间= n/(2Δt+1Δt+3Δt+1Δt+2Δt+(n-1)*3Δt)= n/[9Δt + (n-1)3Δt)]=n/(6Δt +n*3Δt),当n趋向无穷大时,比值为1/3Δt -

第10题:

已知cache存储周期为20ns,主存存储周期为220ns,cache/主存系统平均访问时间为60ns,则cache命中率是()。

正确答案:80% -

第11题:

填空题假设某程序中Load指令占26%,Store指令占9%,则写操作在所有访存操作中所占 的比例为(),写操作在访问数据Cache操作中所占的比例为()。正确答案: 7%,25%解析: 暂无解析 -

第12题:

单选题采用指令Cache与数据Cache分离的主要目的是( )。A减低Cache的缺失损失

B提高Cache的命中率

C减低CPU平均访问时间

D减少指令流水线资源冲突

正确答案: D解析:

把指令Cache与数据Cache分离后,取指和取数分别到不同的Cache中寻找,那么指令流水线中取指部分和取数部分就可以很好的避免冲突,即减少了指令流水线的冲突。 -

第13题:

使用Cache改善系统性能的依据是程序的局部性原理。程序中大部分指令是( )的。设某计算机主存的读/写时间为100ns,有一个指令和数据合一的Cache,已知该Cache的读/写时间为10ns,取指令的命中率为98%,取数的命中率为95%。在执行某类程序时,约有1/5指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置Cache后,每条指令的平均读取时间约为( )ns。

A.顺序存储、顺序执行 B.随机存储、顺序执行 C.顺序存储、随机执行 D.随机存储、随机执行 A.12.3 B.14.7 C.23.4 D.26.3

正确答案:A,B

-

第14题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令( 2△t)、分析指令( 1△t)、取操作数(3△t)、运算(1△t).写回结果 (2△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为(请作答此空) ;若连续向流水线拉入10条指令,则该流水线的加速比为( ) 。 答案:B解析:

答案:B解析:

-

第15题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(3△t)、分析指令(1△t)、取操作数(5△t)、运算(1△t), 写回结果(2△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为( )。 答案:B解析:吞吐率:单位时间内流水线完成的任务数量。

答案:B解析:吞吐率:单位时间内流水线完成的任务数量。

最大吞吐率 =1/max(

),而其中,m是流水线的段数, 是特定过程段执行时间。 -

第16题:

在Cache和主存构成的两级存储系统中,Cache的存取时间为100ns,主存的存取时间为1μs,Cache访问失败后CPU才开始访存。如果希望Cache-主存系统的平均存取时间不超过Cache存取时间的15%,则Cache的命中率至少应为()。A.95%

B.98%

C.98.5%

D.99.5%答案:C解析:设Cache-主存系统的平均存取时间为Cache存取时间的1.15倍时Cache命中率为p,则有100+1000×(1-p)=115,解之得,p=0.985=98.5%。 -

第17题:

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令(2 Δt )、分析指令(1Δt )、取操作数(3Δt )、运算(1Δt )和写回结果(2Δt ) 组成, 并分别用5 个子部件完成,该流水线的执行周期为(请作答此空) ;若连续向流水线输入10条指令,该流水线完成的时间为( )。A.3Δt

B.1Δt

C.2Δt

D.7Δt答案:A解析:流水线的执行周期为流水线执行时间最长的一段。10条指令使用流水线的执行时间=(2Δt+1Δt+3Δt+1Δt+2Δt)+(10-1)*3Δt=36Δt。 -

第18题:

使用 Cache 改善系统性能的依据是程序的局部性原理。程序中大部分指令是( )的。设某计算机主存的读/写时间为 100ns,有一个指令和数据合一的 Cache,已知该 Cache的读/写时间为 10ns,取指令的命中率为 98%,取数的命中率为 95%。在执行某类程序时,约有 1/5 指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置 Cache 后,每条指令的平均读取时间约为(请作答此空)ns。A.顺序存储、顺序执行

B.随机存储、顺序执行

C.顺序存储、随机执行

D.随机存储、随机执行答案:A解析:(100*2%+10*98%)+(100*5%+10*95%)*20%=14.7 -

第19题:

使用 Cache 改善系统性能的依据是程序的局部性原理。程序中大部分指令是(60)的。设某计算机主存的读/写时间为 100ns,有一个指令和数据合一的 Cache,已知该 Cache的读/写时间为 10ns,取指令的命中率为 98%,取数的命中率为 95%。在执行某类程序时,约有 1/5 指令需要额外存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置 Cache 后,每条指令的平均读取时间约为(61)ns。A.12.3

B.14.7

C.23.4

D.26.3答案:B解析:(100*2%+10*98%)+(100*5%+10*95%)*20%=14.7 -

第20题:

某计算机系统采用 5 级流水线结构执行指令,设每条指令的执行由取指令(2 ?t )、分析指令(1?t )、取操作数(3?t )、运算(1?t )和写回结果(2?t ) 组成, 并分别用 5 个子部完成,该流水线的最大吞吐率为() ;若连续向流水线输入 10 条指令,则该流水线的加速比为( 请作答此空) .A. 1:10

B. 2:1

C. 5:2

D. 3:1答案:C解析:本题考察流水线知识,相关计算公式如下:计算机流水线执行周期=最慢那个指令执行时间;流水线执行时间=首条指令执行时间+(指令总数-1)*流水线执行周期;流水线吞吐率=任务数/完成时间;流水线加速比=不采用流水线的执行时间/采用流水线的执行时间;根据公式:流水线执行周期=3?t,流水线执行时间= n/(2?t +1?t +3?t +1?t + 2?t +(n-1)*3?t)=n/[9?t + (n-1)3?t)]=n/(6?t +n*3?t),当n趋向无穷大时,比值为1/3?t10条指令不用流水线的执行时间=(2?t +1?t +3?t +1?t +2?t)*10=90?t。10条指令使用流水线的执行时间=(2?t +1?t +3?t +1?t +2?t)+(10-1)*3?t =36?t。所以加速比为:90?t /36?t =5:2 -

第21题:

假设某程序中Load指令占26%,Store指令占9%,则写操作在所有访存操作中所占 的比例为(),写操作在访问数据Cache操作中所占的比例为()。

正确答案:7%;25% -

第22题:

CPU执行每一条指令都要分成若干步:取指令、指令译码、取操作数、执行运算、保存结果等。CPU在取指令阶段的操作是()

- A、从硬盘读取一条指令并放入内存储器

- B、从内存储器(或cache)读取一条指令放入指令寄存器

- C、从指令寄存器读取一条指令放入指令计数器

- D、从内存储器读取一条指令放入运算器

正确答案:B -

第23题:

问答题某计算机的存储系统由Cache、主存和用于虚拟存储的磁盘组成。CPU总是从Cache中获取数据。若所访问的字在Cache中,则存取它只需要20ns,将所访问的字从主存装入Cache需要60ns,而将它从磁盘装入主存则需要1200us。假定Cache的命中率为90%,主存的命中率为60%,计算该系统访问一个字的平均存取时间。正确答案: 说明:

T.c=20ns//访问Cache时时间,Cache

T.m=60ns//访问主存时间,Memory

T.d=1200us//访问磁盘(外存)时间,Disk

H.90%//Cache-主存层次中,CPU的Cache命中率

H.m=60%//主存-辅存层次中,CPU的主存命中率

T.a//平均访问时间,Average

T.a=h*tc+(1-h)(tc+hm*tm+(1-hm)*(tm+td))

T.a=0.9*20+0.1*Tm=18+0.1*Tm

T.m=20+0.6*60+0.4*(60+1200000)=480080ns

T.a=18+48008=48026ns解析: 暂无解析