用verilog/vddl检测stream中的特定字符串(分状态用状态机写)。(飞利浦-大唐笔试)

题目

用verilog/vddl检测stream中的特定字符串(分状态用状态机写)。(飞利浦-大唐笔试)

相似考题

更多“用verilog/vddl检测stream中的特定字符串(分状态用状态机写)。(飞利浦-大唐笔试)”相关问题

-

第1题:

用逻辑们和cmos电路实现ab+cd。(飞利浦-大唐笔试)

正确答案:

-

第2题:

写异步D触发器的verilog module。(扬智电子笔试) module dff8(clk , reset, d, q); input clk;写异步D触发器的verilog module。(扬智电子笔试)

module dff8(clk , reset, d, q);

input clk;

input reset;

input [7:0] d;

output [7:0] q;

reg [7:0] q;

always @ (posedge clk or posedge reset)

if(reset)

q <= 0;

else

q <= d;

endmodule

正确答案:

-

第3题:

用VERILOG或VHDL写一段代码,实现10进制计数器。(未知)

正确答案:

-

第4题:

画状态机,接受1,2,5分钱的卖报机,每份报纸5分钱。(扬智电子笔试)

正确答案:

-

第5题:

设计一个自动饮料售卖机,饮料10分钱,硬币有5分和10分两种,并考虑找零:(1)

画出fsm(有限状态机);(2)用verilog编程,语法要符合fpga设计的要求;(3)设计

工程中可使用的工具及设计大致过程。(未知)

正确答案:

-

第6题:

用verilog/vhdl写一个fifo控制器(包括空,满,半满信号)。(飞利浦-大唐笔试)

正确答案:

-

第7题:

如何解决亚稳态。(飞利浦-大唐笔试)

正确答案:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

-

第8题:

2)用verilog编程,语法要符合fpga设计

的要求。(未知)

正确答案:

-

第9题:

()是用来反映代码的物理结构。A.构件图

B.用例图

C.类图

D.状态机

参考答案:A

-

第10题:

UML行为模型的状态图是以状态机模型的方式进行的用例实现。状态图只能用来实现单个用例。

正确答案:错误 -

第11题:

()是用来反映代码的物理结构。

- A、构件图

- B、用例图

- C、类图

- D、状态机

正确答案:A -

第12题:

判断题UML行为模型的状态图是以状态机模型的方式进行的用例实现。状态图只能用来实现单个用例。A对

B错

正确答案: 错解析: 暂无解析 -

第13题:

画出DFF的结构图,用verilog实现之。(威盛)

正确答案:

-

第14题:

用D触发器实现2倍分频的Verilog描述? (汉王笔试)

正确答案:

module divide2( clk , clk_o, reset);

input clk , reset;

output clk_o;

wire in;

reg out ;

always @ ( posedge clk or posedge reset)

if ( reset)

out <= 0;

else

out <= in;

assign in = ~out;

assign clk_o = out;

endmodule

-

第15题:

一个状态机的题目用verilog实现(不过这个状态机画的实在比较差,很容易误解的)。(威盛VIA 2003.11.06 上海笔试试题)

正确答案:

-

第16题:

设计一个自动售货机系统,卖soda水的,只能投进三种硬币,要正确的找回钱数。(1)画出fsm(有限状态机);(2)用verilog编程,语法要符合fpga设计的要求。(未知)

正确答案:

-

第17题:

画出可以检测10010串的状态图,并verilog实现之。(威盛)

正确答案:

-

第18题:

用一种编程语言写n!的算法。(威盛VIA 2003.11.06 上海笔试试题)

正确答案:

-

第19题:

给了reg的setup,hold时间,求中间组合逻辑的delay范围。(飞利浦-大唐笔试)

正确答案:Delay < period - setup – hold

-

第20题:

请教:飞利浦笔试试题第1大题第1小题如何解答?【题目描述】

1.用逻辑门和cmos 电路实现ab+cd。

【参考答案分析】。。。。。。。。。。。。。。。。 -

第21题:

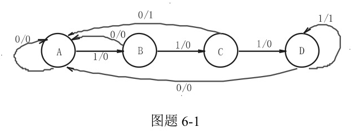

用文字 描述图题6-1所示的状态图,并说明是何种类型状态机。

答案:状态A:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态B,输出0状态B:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态C,输出0状态C:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态D,输出0状态D:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态D,输出1该状态为梅里状态机。

答案:状态A:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态B,输出0状态B:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态C,输出0状态C:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态D,输出0状态D:如果输入为0,转移到状态A,输出0如果输入为1,转移到状态D,输出1该状态为梅里状态机。

-

第22题:

基本呼叫状态模型BCSM是用有限状态机描述建立/维持呼叫的动作

正确答案:正确 -

第23题:

单选题()是用来反映代码的物理结构。A构件图

B用例图

C类图

D状态机

正确答案: D解析: 暂无解析