一个四体并行的低位交叉编址存储器,每个存储体的存取周期为200ns,总线传输周期为50ns,则连续读取10个存储字需时()。A.2000ns B.600ns C.650ns D.300ns

题目

B.600ns

C.650ns

D.300ns

相似考题

参考答案和解析

更多“一个四体并行的低位交叉编址存储器,每个存储体的存取周期为200ns,总线传输周期为50ns,则连续读取10个存储字需时()。”相关问题

-

第1题:

假设某计算机有1MB的内存,并按字节编址,为了能存取其中的内容,其地址寄存器至少需要(9)位。为使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,一个字的地址码应(10)。若存储周期为200ns,且每个周期访问 4B,则该存储器的带宽为(11)bit/s。假如程序员可用的存储空间为4MB,则程序员所用的地址为(12),而真正访问内存的地址为(13)。

A.10

B.16

C.20

D.32

正确答案:C

-

第2题:

假设某计算机具有1 MB的内存(目前使用的计算机往往具有128 MB以上的内存),并按字节编址,为了能存取该内存各地址的内容,其地址寄存器至少需要二进制(42)位。为了使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,1字节的地址码应(43)。若存储器周期为200ns,且每个周期可访问4字节,则该存储器带宽为(44)b/s。假如程序员可用的存储空间为4MB,则程序员所用的地址为(45),而真正访问内存的地址称为(46)。

A.10

B.16

C.20

D.32

正确答案:C

-

第3题:

设某存储器总线的工作频率为100MHz,数据宽度为16位,每个总线周期传输2次,其带宽为___【19】___MB/S,1分钟可传输___【20】___MB数据。

正确答案:400 24000

-

第4题:

存储器是计算机系统的记忆设备,它主要用于存放(1),而存储单元是指一(2)。存储器系统由分布在计算机各个不同部件的多种存储设备组成:位于CPU内部的寄存器,以及用于CPU的控制存储器。内部存储器是可以被处理器直接存取的存储器,又称为主存储器。它主要由(3)半导体存储器构成。存储器系统的性能主要由存取时间、存储器带宽、存储器周期和数据传输率等来衡量,其中存储周期指的是(4)。若一存储器的存储器周期是500ns,而每个周期可访问4字节。则该存储器的带宽是(5)。

A.程序

B.微程序

C.数据

D.三者均正确

正确答案:D

解析:存储器是计算机系统的记忆设备,它主要用于存放程序和数据,而存储单元是指存储一个机器字所需的单元集合。存储器系统由分布在计算机各个不同部件的多种存储设备组成:位于CPU内部的寄存器,以及用于CU的控制存储器。内部存储器是可以被处理器直接存取的存储器,又称为主存储器,它主由随机访问存储器RAM构成。存储器系统的性能主要由存取时间、存储器带宽、存储器周期和数据传输率等来衡量,其中存储周期一个存储器周期就等于两次相邻的存取之间所需的时间,即存储器进行连续读或写操作所允许的最短时间间隔。存储器带宽是指每秒钟能访问的位数。若一存储器的存储器周期是500ns,而每个周期可访问4字节,则该存储器的带宽=4×8b/500ns=64Mbit/s -

第5题:

存储器的带宽决定了以存储器为中心的机器获得信息的速度,为了提高存储器带宽,可以采用

A.缩短存取周期

B.增加存储字长

C.增加存储体

D.提高CPU主频

E.增加CPU内总线位数

正确答案:ABC

-

第6题:

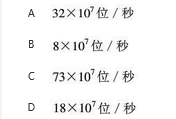

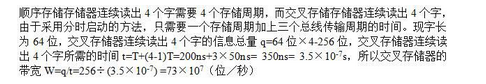

设存储器容量为32字,字长64位,模块数m=4,存储周期T=200ns,数据总线宽度为64位,总线传送周期τ=50ns。用交叉方式进行组织,交叉存储器的带宽是()。 答案:C解析:

答案:C解析:

-

第7题:

假设某计算机具有1MB的内存,并按字节编址,为了能存取该内存各地址的内容,其地址寄存器至少需要二进制(1)位。为使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,一个字的地址码应(2)。若存储周期为200ns,且每个周期可访问4个字节,则该存储器带宽为(3)bps。假如程序员可用的存储空间为4MB,则程序员所用的地址为(4),而真正访问内存的地址为(5)。空白(1)处应选择()

- A、10

- B、16

- C、20

- D、32

正确答案:C -

第8题:

并行存储器有哪几种编址方式? 简述低位交叉编址存储器的工作原理。

正确答案:并行存储器有单体多字、多体单字和多体多字等几种系统。多体交叉访问存储器可分为高位交叉编址存储器和低位交叉编址存储器。低位交叉编址又称为横向编址,连续的地址分布在相邻的存储体中,而同一存储体内的地址都是不连续的。存储器地址寄存器的低位部分经过译码选择不同的存储体,而高位部分则指向存储体内的存储字。如果采用分时启动的方法,可以在不改变每个存储体存取周期的前提下,提高整个主存的速度。 -

第9题:

如果存储器周期是400ns,而每个周期可访问4字节,则存储器带宽为()。

正确答案:80Mbps -

第10题:

问答题并行存储器有哪几种编址方式? 简述低位交叉编址存储器的工作原理。正确答案: 并行存储器有单体多字、多体单字和多体多字等几种系统。多体交叉访问存储器可分为高位交叉编址存储器和低位交叉编址存储器。低位交叉编址又称为横向编址,连续的地址分布在相邻的存储体中,而同一存储体内的地址都是不连续的。存储器地址寄存器的低位部分经过译码选择不同的存储体,而高位部分则指向存储体内的存储字。如果采用分时启动的方法,可以在不改变每个存储体存取周期的前提下,提高整个主存的速度。解析: 暂无解析 -

第11题:

问答题一个4体低位交叉的存储器,假设存储周期为T,CPU每隔1/4存取周期启动一个存储体,试问依次访问64个字需多少个存取周期?正确答案: 4体低位交叉的存储器的总线传输周期为τ,τ=T/4,依次访问64个字所需时间为:t=T+(64-1)τ=T+63T/4=16.75T解析: 暂无解析 -

第12题:

填空题如果存储器周期是400ns,而每个周期可访问4字节,则存储器带宽为()。正确答案: 80Mbps解析: 暂无解析 -

第13题:

如存储器的工作频率为333MHz,数据线宽度为32位,每个周期传输1次数据,则存储器的带宽=___【23】____MB/s。若存储器总线采用串行总线,以10位为一个数据帧(包含一个字节的存储数据),则总线带宽=总线频率/___【24】____。

正确答案:1332 10

-

第14题:

存储器的带宽是指每秒可传输(读出/写入)的最大数据总量。存储器带宽与存储器总线的工作___【19】____有关,也与数据线的___【20】____和每个总线周期的传输次数有关。

正确答案:频率周期 位数位宽

-

第15题:

假设某计算机具有1MB的内存(目前使用的计算机往往具有64MB以上的内存),并按字节编址,为了能存取该内存各地址的内容,其地址寄存器至少需要二进制(86)位。为使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,一个字的地址码应(87)。若存储周期为200ns,且每个周期可访问4字节,则该存储器带宽为(88)b/s。假如程序员可用的存储空间为4MB,则程序员所用的地址为(89),而真正访问内存的地址称为(90)。

A.10

B.16

C.20

D.32

正确答案:C

-

第16题:

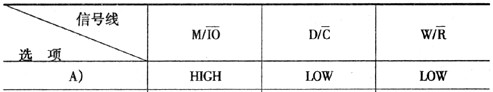

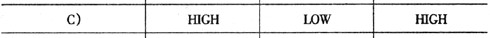

80386有4个总线周期定义信号

但主要的总线周期定义了前三个。在I/O写周期,总线周期定义信号状态为( ),在存储器数据读取周期总线信号定义为( ),在存储器指令码读取周期总线信号定义为( )。

A.

B.

C.

D.

正确答案:ABD

正确答案:ABD

解析:首先需清楚这三个信号的含义,M/信号表示目前被操作的对象是存储器还是I/O,信号为高电平代表是存储器,低电平代表为I/O。信号是区别对所进行的操作对象是数据的存取还是实施控制,高电平代表存取数据,低电平代表控制(包括暂停、中断认可、读取指令码等)。W/R则代表正在进行的操作是写还是读。 -

第17题:

已知单个存储体的存储周期为110ns,总线传输周期为10ns,则当采用低位交叉编址的多模块存储器时,存储体数应()。A.小于11

B.等于11

C.大于11

D.大于等于11答案:D解析:为了保证第二次启动某个体时,它的上次存取操作已完成,存储体的数量应大于等于11(110ns/10ns=11)。 -

第18题:

设存储器容量为32位,字长64位,模块数m=8,分别用顺序方式和交叉方式进行组织。若存储周期T = 200ns,数据总线宽度为64位,总线传送周期为50ns,则顺序存储器和交叉存储器带宽各是多少?

略 -

第19题:

一个4体低位交叉的存储器,假设存储周期为T,CPU每隔1/4存取周期启动一个存储体,试问依次访问64个字需多少个存取周期?

正确答案:4体低位交叉的存储器的总线传输周期为τ,τ=T/4,依次访问64个字所需时间为:t=T+(64-1)τ=T+63T/4=16.75T -

第20题:

下面关于内存储器(也称为主存)的叙述中,正确的是()。

- A、内存储器和外存储器是统一编址的,字是存储器的基本编址单位

- B、内存储器与外存储器相比,存取速度慢、价格便宜

- C、内存储器与外存储器相比,存取速度快、价格贵

- D、RAM和ROM在断电后信息将全部丢失

正确答案:C -

第21题:

假设某计算机具有1MB的内存,并按字节编址,为了能存取该内存各地址的内容,其地址寄存器至少需要二进制(1)位。为使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,一个字的地址码应(2)。若存储周期为200ns,且每个周期可访问4个字节,则该存储器带宽为(3)bps。假如程序员可用的存储空间为4MB,则程序员所用的地址为(4),而真正访问内存的地址为(5)。空白(4)处应选择()

- A、有效地址

- B、程序地址

- C、逻辑地址

- D、物理地址

正确答案:C -

第22题:

单选题某存储器按字节编址,要求数据传输率达到8×106字节/秒,则应选用存储周期为()的存储芯片。A800ns

B250ns

C200ns

D120ns

正确答案: D解析: 暂无解析 -

第23题:

单选题假设某计算机具有1MB的内存,并按字节编址,为了能存取该内存各地址的内容,其地址寄存器至少需要二进制(1)位。为使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,一个字的地址码应(2)。若存储周期为200ns,且每个周期可访问4个字节,则该存储器带宽为(3)bps。假如程序员可用的存储空间为4MB,则程序员所用的地址为(4),而真正访问内存的地址为(5)。空白(2)处应选择()A最低两位为00

B最低两位为10

C最高两位为00

D最高两位为10

正确答案: C解析: 暂无解析