在Cache存储器中,CPU每次写Cache的同时,也写入主存,称这种更新主存块内容的方法为()法。

题目

在Cache存储器中,CPU每次写Cache的同时,也写入主存,称这种更新主存块内容的方法为()法。

相似考题

更多“在Cache存储器中,CPU每次写Cache的同时,也写入主存,”相关问题

-

第1题:

CPU在执行写操作时,把数据同时写入Cache和主存指的是()。A.写直达法

B.写回法

C.抵触修改法

正确答案:A

-

第2题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

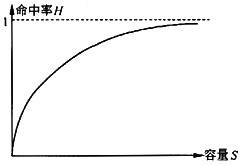

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来动态存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况;当发生Cache块失效时,所采用的替换算法;Cache的容量;在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等等。Cache的命中率随其容量增加而提高,它们之间的关系曲线如下图所示。在Cache容量比较小的时候,命中率提高的非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这是实际上是做不到的。

-

第3题:

在多级存储系统中,Cache处在CPU和主存之间,解决(55)问题。若Cache和主存的存取时间分别为T1和T2,Cache的命中率为H,则该计算机实际存取时间为(56)。当CPU向存储器执行读操作时,首先访问Cache,若命中,则从Cache中取出指令或数据,否则从主存中取出,送(57):当CPU向存储器执行写操作时,为了使Cache的内容和主存的内容保持一致,若采用(58)法,则同时写入Cache和主存。由于Cache容量比主存容量小,因此当Cache满时,执行把主存信息向Cache写入,就要淘汰Cache中已有的信息,为了提高Cache的命中率,采用一种(59)替换算法。

A.主存容量扩充

B.主存和CPU速度匹配

C.多个请求源访问主存

D.BIOS存放

正确答案:B

解析:he的主要功能是提供CPU与RAM间的速度匹配问题,存储器效率的计算公式为:HTI+(1-H)T2。为了提高Cache的命中率,我们常采用LRU最近最少使用的替换算法。 -

第4题:

下面是关于CPU与主存储器之间的Cache的叙述,其中正确的是( )。

A.Cache中存放的主存储器中某一部分内容的映象

B.Cache能由用户直接访问

C.位于主板上的12 Cache要比与CPU封装在一起的L1 Cache速度快

D.Cache存储器的功能不全由硬件实现

正确答案:A

-

第5题:

若Cache和主存的存取时间分别为T1和T2,Cache的命中率为H,则该计算机的实际存取时间为(2)。当CPU向存储器执行读操作时,首先访问Cache,如命中,则从Cache中取出指令或数据,否则从主存中取出,送(3);当CPU向存储器执行写操作时,为了使Cache内容和主有的内容保持一致,若采用(4)法,同时写入Cache和主存。

A.H×T1+T2

B.(1-H×T1)+H×T2

C.T2-H×T1

D.H×T1+(1-H)×T2

正确答案:D

解析:Cache的命中率为H,则访问内存概率为1-H,因此实际存取时间为H×T1+(1-H)×T2。 -

第6题:

在Cache实现的两种写策略中,()的速度快,“写”操作能以Cache存储器速度进行,访存次数少;采用()总能保持Cache和主存内容的一致。

正确答案:写回法;写直达法 -

第7题:

下面是主存储器和CAChe的比较,正确的有()

- A、微机主存储器多数采用半导体动态存储器(DRAM),CAChe采用半导体静态存储器(SRAM)。这两种存储器中的信息均不能长期保留

- B、CPU访问主存储器的速度快于访问CAChe的速度

- C、在配有CAChe的计算机中,CPU每次访问存储器都首先访问CAChe,若欲访问的数据在CAChe中,则访问结束,否则,再访问主存储器,并把有关数据取人CAChe

- D、CAChe容量一般都小于主存储器

正确答案:A,C,D -

第8题:

对于Cache的两种写策略,执行“写”操作时,只写入Cache,仅当Cache中相应的块被替换时,才写回主存,称为()。执行“写”操作时,不仅写入Cache,而且也写入下一级存储器,称为()。

正确答案:写回法;写直达法 -

第9题:

在PC机中,各类存储器的速度由高到低的次序是()。

- A、主存、Cache、硬盘、软盘

- B、硬盘、Cache、主存、软盘

- C、Cache、硬盘、主存、软盘

- D、Cache、主存、硬盘、软盘

正确答案:D -

第10题:

多选题下面是主存储器和CAChe的比较,正确的有()A微机主存储器多数采用半导体动态存储器(DRAM),CAChe采用半导体静态存储器(SRAM)。这两种存储器中的信息均不能长期保留

BCPU访问主存储器的速度快于访问CAChe的速度

C在配有CAChe的计算机中,CPU每次访问存储器都首先访问CAChe,若欲访问的数据在CAChe中,则访问结束,否则,再访问主存储器,并把有关数据取人CAChe

DCAChe容量一般都小于主存储器

正确答案: C,A解析: 暂无解析 -

第11题:

填空题在Cache存储器中,CPU每次写Cache的同时,也写入主存,称这种更新主存块内容的方法为()法。正确答案: 写直达解析: 暂无解析 -

第12题:

填空题Cache存储器写操作时,只写入Cache,仅当需要块替换时,才将其写回主存,称这种修改主存块内容的方法为()法。正确答案: 写回解析: 暂无解析 -

第13题:

在CPU和主存间设置cache存储器主要是为了(14)。若使用基于数据内容进行访问的存储设备作为cache时,能更快决定是否命中。这种地址映射方法称为(15)映射。CPU向cache执行写操作时,可以同时写回主存储器或者仅当cache中该数据被淘汰时才写回主存储器,前者称为(16),而后者称为(17)。若cache的存取速度是主存存取速度的10倍,且命中率可达到0.8,则CPU对该存储系统的平均存取周期为(18)T(T为主有的存取周期)。

A.扩充主存容量

B.解决CPU和主存的速度匹配

C.提高可靠性

D.增加CPU访问的并行度

正确答案:B

-

第14题:

关于Cache(高速缓冲存储器)的说法中,错误的是(9)。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

正确答案:D

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对 Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况:当发生Cache块失效时,所采用的替换算法:Cache的容量:在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等。Cache的命中率随它的容量的增加而提高,它们之间的关系曲线见下图所示。在 Cache容量比较小的时候,命中率的提高得非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这实际上是做不到的。

-

第15题:

计算机中有cache存储器、主存、外存等多种存储器,用以保证其性能/价格比的优化。下列关于存储器的叙述中,错误的是

A.主存容量通常比外存小,但存取速度较快

B.主存的存取周期越长,存取速度就越快

C.cache存储器大多已集成在CPU芯片中

D.cache存储器直接供CPU存取数据,减少了CPU的等待时间

正确答案:B

-

第16题:

在分析Cache对机器性能的影响时,正确的叙述是( )。

A.Cache容量比主存小许多,决定机器访问存储器速度的是主存,Cache只起次要作用

B.CPU访问存储器时不受Cache控制器的控制

C.Cache存储器中保存着CPU当前频繁访问的指令代码和数据

D.奔腾PC机采用两极Cache结构,一级放指令,一级放数据

正确答案:C

-

第17题:

Cache存储器写操作时,只写入Cache,仅当需要块替换时,才将其写回主存,称这种修改主存块内容的方法为()法。

正确答案:写回 -

第18题:

下面是关于CPU访问主存和高速缓存CAChe关系描述,正确的有()

- A、没有CAChe的微机,只有主存能与CPU直接进行信息交换

- B、拥有CAChe的微机,CAChe和主存都能直接与CPU交换信息

- C、一台装有CAChe的微机,CPU从外存读人数据的顺序是外存→主存→CAChe

- D、CAChe使用的是半导体动态存储器,所以其中的信息不能长期保留

正确答案:A,C -

第19题:

以下关于CPU与主存之间增加高速缓存(Cache)的叙述中,错误的是()。

- A、Cache扩充了主存储器的容量

- B、Cache可以降低由于CPU与主存之间的速度差异造成的系统性能影响

- C、Cache的有效性是利用了对主存储器访问的局部性特征

- D、Cache中通常保存着主存储器中部分内容的一份副本

正确答案:A -

第20题:

当访问Cache系统失效时,通常不仅主存向CPU传送信息,同时还需要将信息写入Cache,在此过程中传送和写入信息的数据宽度各为()。

- A、块、页

- B、字、字

- C、字、块

- D、块、块

正确答案:C -

第21题:

填空题对于Cache的两种写策略,执行“写”操作时,只写入Cache,仅当Cache中相应的块被替换时,才写回主存,称为()。执行“写”操作时,不仅写入Cache,而且也写入下一级存储器,称为()。正确答案: 写回法,写直达法解析: 暂无解析 -

第22题:

多选题下面是关于CPU访问主存和高速缓存CAChe关系描述,正确的有()A没有CAChe的微机,只有主存能与CPU直接进行信息交换

B拥有CAChe的微机,CAChe和主存都能直接与CPU交换信息

C一台装有CAChe的微机,CPU从外存读人数据的顺序是外存→主存→CAChe

DCAChe使用的是半导体动态存储器,所以其中的信息不能长期保留

正确答案: A,D解析: 暂无解析 -

第23题:

填空题在Cache实现的两种写策略中,()的速度快,“写”操作能以Cache存储器速度进行,访存次数少;采用()总能保持Cache和主存内容的一致。正确答案: 写回法,写直达法解析: 暂无解析