假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线

题目

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线

相似考题

参考答案和解析

更多“假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线”相关问题

-

第1题:

在下列不同结构的处理机上执行6x6的矩阵乘法C:A×B,计算所需要的最短时间。只计算乘法指令和加法指令的执行时间,不计算取操作数、数据传送和程序控制等指令的执行时间。加法部件和乘法部件的延迟时间都是3个时钟周期,另外,加法指令和乘法指令还要经过“取指令”和“指令译码”的时钟周期,每个时钟周期为20ns,C的初始值为“0”。各操作部件的输出端有直接数据通路连接到有关操作部件的输入端,在操作部件的输出端设置有足够容量的缓冲寄存器。如果处理机内只有一个通用操作部件,采用顺序方式执行指令,那么所需要的时间为(5)。如果单流水线标量处理机,有一条两个功能的静态流水线,流水线每个功能段的延迟时间均为一个时钟周期,加法操作和乘法操作各经过3个功能段,那么所需要的时间为(6)。

A.105.6ms

B.52.8ms

C.39.6ms

D.72.8ms

正确答案:C

-

第2题:

下列关于超标量(Superscalar)技术的叙述,错误的是

A.超标量技术通过内置多条流水线来同时执行多个处理

B.超标量技术的实质是以空间换取时间

C.在经典奔腾中,由两条整数指令流水线和一条浮点指令流水线组成

D.流水线U和流水线V既可以执行精简指令义可以执行复杂指令

正确答案:D

解析:流水线U既可以执行精简指令又可以执行复杂指令,而流水线V只能执行精简指令。 -

第3题:

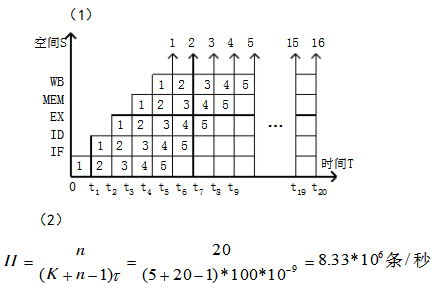

某计算机系统采用5级流水线结构执行指令,设每条指令的执行由取指令( 2△t)、分析指令( 1△t)、取操作数(3△t)、运算(1△t).写回结果 (2△t)组成,并分别用5个子部件完成,该流水线的最大吞吐率为(请作答此空) ;若连续向流水线拉入10条指令,则该流水线的加速比为( ) 。 答案:B解析:

答案:B解析:

-

第4题:

下列关于流水线方式执行指令的叙述中,不正确的是( )。A.流水线方式可提高单条指令的执行速度

B.流水线方式下可同时执行多条指令

C.流水线方式提高了各部件的利用率

D.流水线方式提高了系统的吞吐率答案:A解析:流水线(pipeline)技术是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。流水线是Intel首次在486芯片中开始使用的。在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。经典奔腾每条整数流水线都分为四级流水,即取指令、译码、执行、写回结果,浮点流水又分为八级流水。 -

第5题:

在高速计算机中,广泛采用流水线技术。例如,可以将指令执行分成取指令、分析指令和执行指令3个阶段,不同指令的不同阶段可以(1)执行;各阶段的执行时间最好(2);否则在流水线运行时,每个阶段的执行时间应取(3)。空白(2)处应选择()

- A、为0

- B、为1个周期

- C、相等

- D、不等

正确答案:C -

第6题:

假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?插入三个流水段寄存器,得到一个四级流水线

正确答案:三个流水段寄存器分别插在A和B、C和D、D和E之间,这样第一个流水段的组合逻辑延时为80ps,第二段时延为30+60=90ps,第三段时延为50ps,最后一段延时为70+10=80ps。这样每个流水段都以最长延时调整为90+20=110ps,故时钟周期为110ps,指令吞吐率为1/110ps=9.09GOPS,每条指令的执行时间为4x110=440ps。 -

第7题:

CPU中有一条以上的流水线且每个时钟周期可以完成一条以上指令的技术是()

- A、流水线技术

- B、超流水线技术

- C、倍频技术

- D、超标量技术

正确答案:D -

第8题:

关于经典奔腾的U、V流水线,说法不正确的是()

- A、它们都是整数指令流水线,但是功能不同

- B、两条流水线同时工作时,流水线U可执行复杂指令,流水线V只能执行精简指令

- C、它们属于以空间换取时间的超标量技术

- D、它们各有自己的算术逻辑单元,地址生成电路及Cache接口

正确答案:B -

第9题:

多选题CPU内使用流水线技术后,下列说法可能的是()A取指令和执行指令同步进行

B取指令和执行指令异步进行

C正在执行的指令与流水线中的指令冲突

D流水线内的指令无效

E流水线取指与执行的指令有关

F流水线取指与执行的指令无火

正确答案: B,C解析: 由于流水线取指由各功能部件独立完成,囚此CPU内使用流水线技术后,可能的是取指令和执行指令同步进行、正在执行的指令与流水线中的指令冲突、流水线内的指令无效、流水线取指与执行的指令有关或流水线取指与执行的指令无关;不可能的是取指令和执行指令异步进行,因此A、C、D、E、F是正确答案。 -

第10题:

单选题若某计算机最复杂指令的执行需要完成5个子功能,分别由功能部件A~E实现,各功能部件所需要时间分别为80ps、50ps、50ps、70ps和50ps,采用流水线方式执行指令,流水段寄存器延时为20ps,则CPU时钟周期至少为( )。A60ps

B70ps

C80ps

D100ps

正确答案: D解析:

计算机在一个时钟周期内完成A~E中的一个功能,现在流水段寄存器延时为20ps,则实际上功能部件A~E所需时间依次加20ps,即100ps、70ps、70ps、90ps、70ps。为满足要求CPU的时钟周期至少要大于这5个时间中的最大值,故CPU时钟周期至少为100ps。 -

第11题:

单选题某CPU主频为1.03GHz,采用4级指令流水线,每个流水段的执行需要1个时钟周期。假定CPU执行了100条指令,在其执行过程中没有发生任何流水线阻塞,此时流水线的吞吐率为( )。A0.25×109条指令/秒

B0.97×109条指令/秒

C1.0×109条指令/秒

D1.03×109条指令/秒

正确答案: D解析:

采用4级指令流水线执行100条指令,在执行过程中共用4+(100-1)=103个时钟周期。CPU的主频是1.03GHz,也就是说每秒钟有1.03G个时钟周期。流水线的吞吐率为1.03G×100/103=1.0×109条指令/秒,故答案为C。 -

第12题:

问答题假定最复杂的一条指令所用的组合逻辑分成6块,依次为A~F,其延迟分别为80ps、30ps、60ps、50ps、70ps、10ps。在这些组合逻辑块之间插入必要的流水段寄存器就可实现相应的指令流水线,寄存器延迟为20ps。理想情况下,以下各种方式所得到的时钟周期、指令吞吐率和指令执行时间各是多少?应该在哪里插入流水线寄存器?吞吐量最大的流水线正确答案: 因为所有组合逻辑块中最长延时为80ps,所以,达到最大可能吞吐率的划分应该是以一个流水段延时为80ps+20ps来进行,因此,至少按五段来划分,分别把流水段寄存器插在A和B、B和C、C和D、D和E之间,这样第一段的组合逻辑延时为80ps,第二段为30ps,第三段为60ps,第四段为50ps,最后一段为70+10=80ps。这样每个流水段都以最长延时调整为80+20=100ps,故时钟周期为100ps,指令吞吐率为1/100ps=10GOPS,每条指令的执行时间为5x100=500ps。解析: 暂无解析 -

第13题:

具有两条指令流水线的CPU,一般情况下,每个时钟周期可以执行( )。

A.一条指令

B.二条指令

C.三条指令

D.四条指令

正确答案:B

-

第14题:

在指令流水线中,最大吞吐率是指

A.流水线上所完成指令的最大数量

B.流水线达到稳定状态后可获得的吞吐率

C.流水线上所完成指令或输出结果的数量

D.流水线工作中能达到的吞吐率

正确答案:B

-

第15题:

下列关于RISC机的说法中错误的是()。A.指令长度固定,指令格式种类少,寻址方式种类少

B.配备大量通用寄存器

C.强调采用流水线技术进行优化

D.较少使用硬布线逻辑实现答案:D解析:ABC项都是RISC机的特点,D项,RISC机由于指令结构较简单,故常采用速度较快的硬布线逻辑来实现。 -

第16题:

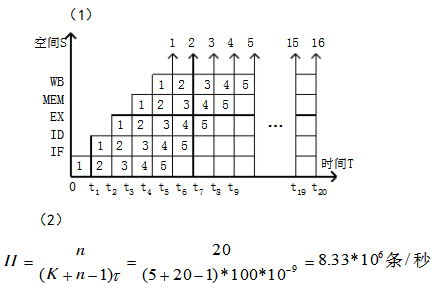

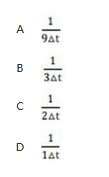

指令流水线右取指(IF) 、译码(ID)、执行 (EX) 、访存(MEM)、写回寄存器堆(WB)五个过程段,共有20条指令连续输入此流水线。 (1)画出流水处理的时空图,假设时钟周期为100ns。 (2)求流水线的实际吞吐率(单位时间里执行完毕的指令数)。

略 -

第17题:

假定某计算机工程师想设计一个新CPU,一个典型程序的核心模块有一百万条指令,每条指令执行时间为100ps。实际流水线并不是理想的,流水段间数据传送会有额外开销。这些开销是否会影响指令执行时间(Instruction latency)和指令吞吐率(Instruction throughput)?

正确答案:流水线段之间数据的传递产生的额外开销,使得一条指令的执行时间被延长,即影响Instruction latency;同时也拉长了每个流水段的执行时间,即影响Instruction throughput。 -

第18题:

下列描述不属于RISC计算机的特点的是()

- A、流水线每周期前进一步

- B、更多通用寄存器

- C、指令长度不固定,执行需要多个周期

- D、独立的Load和Store指令完成数据在寄存器和外部存储器之间的传输

正确答案:C -

第19题:

什么是指令流水线?为什么要引入指令流水线?实现指令流水线操作需要哪些硬件支持?

正确答案:指令的并行操作,或者说指令的重叠执行称为指令流水线操作。引入指令流水线是为了充分利用计算机的资源,例如在 CPU执行指令期间,总线是空闲的,可用来预取后续指令。实现指令流水线操作,需要有指令预取队列和相应的控制逻辑等硬件支持。 -

第20题:

CPU内使用流水线技术后,下列说法可能的是()

- A、取指令和执行指令同步进行

- B、取指令和执行指令异步进行

- C、正在执行的指令与流水线中的指令冲突

- D、流水线内的指令无效

- E、流水线取指与执行的指令有关

- F、流水线取指与执行的指令无火

正确答案:A,C,D,E,F -

第21题:

填空题在理想的情况下,一条k段流水线(每条指令执行k个周期),执行n条指令共()周期。正确答案: 需要k+n-1解析: 暂无解析 -

第22题:

单选题下列描述不属于RISC计算机的特点的是()A流水线每周期前进一步

B更多通用寄存器

C指令长度不固定,执行需要多个周期

D独立的Load和Store指令完成数据在寄存器和外部存储器之间的传输

正确答案: B解析: 暂无解析 -

第23题:

单选题下列关于指令流水线数据通路的叙述中,错误的是( )。A包含生成控制信号的控制部件

B包含算术逻辑运算部件(ALU)

C包含通用寄存器组合取指部件

D由组合逻辑电路和时序逻辑电路组合而成

正确答案: A解析:

五阶段流水线可分为取指IF、译码/取数ID、执行EXC、存储器读MEM、写回Write Back。数字系统中,各个子系统通过数据总线连接形成的数据传送路径称为数据通路,包括程序计数器、算术逻辑运算部件、通用寄存器组、取指部件等等,不包括控制部件,所以A项错误。